Vaibbhav Taraate

# Digital Design Techniques and Exercises

A Practice Book for Digital Logic Design

## Digital Design Techniques and Exercises

### Vaibbhay Taraate

# Digital Design Techniques and Exercises

A Practice Book for Digital Logic Design

Vaibbhav Taraate VLSI Design 1 Rupee S T (Semiconductor Training @ Rs.1) Pune, Maharashtra, India

ISBN 978-981-16-5954-6 ISBN 978-981-16-5955-3 (eBook) https://doi.org/10.1007/978-981-16-5955-3

© The Editor(s) (if applicable) and The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd. 2022

This work is subject to copyright. All rights are solely and exclusively licensed by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Singapore Pte Ltd. The registered company address is: 152 Beach Road, #21-01/04 Gateway East, Singapore 189721, Singapore

Dedicated to my Inspiration Respected Bharat Ratna J. R. D. Tata and Ratan Tata

### **Preface**

The understanding of the digital design elements and their role in the design of the digital system is especially important to the logic designers, system design engineers, RTL design engineers and even to the ASIC/FPGA design engineers.

There are many evolutions in the digital design during the past century, and the main objective of this book is to have a discussion on the important design techniques useful in the digital design.

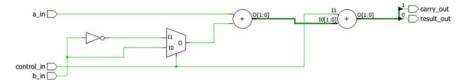

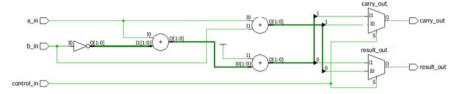

The book has 12 chapters and is mainly useful to understand about the digital design techniques, FSM-based designs, design optimization, data and control path designs, timing of the design, area and speed requirements and optimization during logic design phase. Few of the logic diagrams and timing sequences are captured using xilinx ISE and Vivado tools. For more information about the FPGA EDA tools please visit www.xilinx.com!

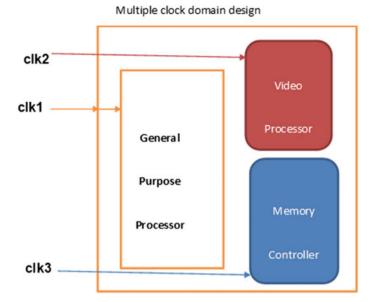

The book even covers the advanced concepts like architecture design, multiple clock domain designs, multiple power domains, system design and interfacing techniques.

The book has exercises at the end of each chapter and is useful to apply the design concepts.

Chapter 1 "Basics of Digital Design" discusses about the basics of the digital design elements, Boolean function implementation techniques and main important goals during the design.

Chapter 2 "Design Using Universal Logic" the universal logic elements and their use in the design aer discussed. The chapter discusses about the cascade and parallel logic and the design techniques to improve the speed of the design and to optimize for the area.

Chapter 3 "Combinational Design Resources" discusses about the various code converters, combinational design resources and the arithmetic resources. The design techniques discussed are useful to design the combinational or glue logic. The chapter even focuses on the various performance improvement techniques and their use to design the combinational logic.

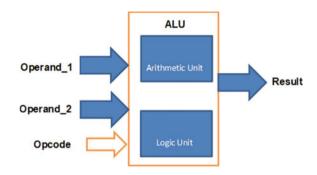

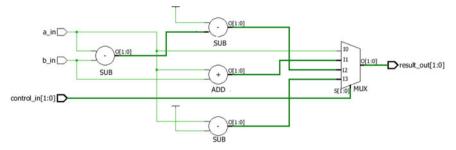

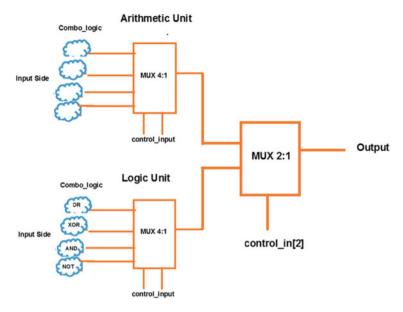

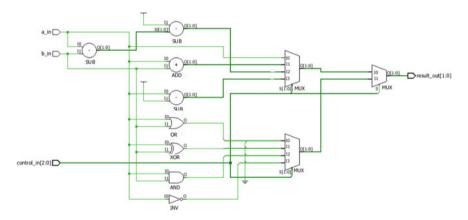

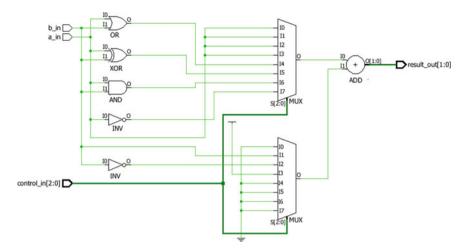

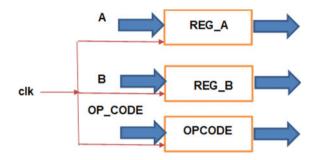

Chapter 4 "Case Study: ALU Design" discusses about the use of the combinational resources and arithmetic elements to design the digital circuits. The objective is to

viii Preface

optimize the design to have the least area and maximum speed. The chapter discusses about the basics of the instruction processing and the optimization for the area and speed.

Chapter 5 "Practical Scenarios and the Design Techniques" discusses about the parallel versus cascade, priority logic and their use in the design. The design of the combinational logic using the decoders and encoders is also discussed in this chapter.

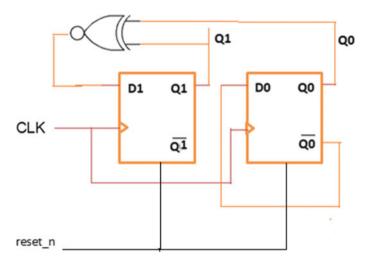

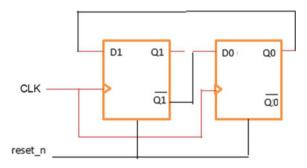

Chapter 6 "Basics of the Sequential Design," the sequential design elements are latches and flip-flops and they are extensively used in the design. The latch-based designs and flip-flop-based designs and their applications are discussed in this chapter.

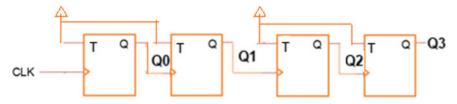

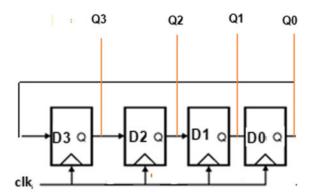

Chapter 7 "Sequential Design Techniques" discusses about the various techniques useful to implement the sequential designs. The goal is to have the sequential design which has lesser area, maximum speed and low power. The chapter is useful to understand the sequential design techniques to design the counters, registers with the goal of area and speed optimization.

Chapter 8 "Important Design Scenarios" discusses the important design scenarios and techniques useful to design the sequential logic. The chapter is useful to understand about the duty cycle and how to design the sequential circuits with the goal to have duty cycle control.

Chapter 9 "FSM Design Techniques" discusses about the FSM design techniques and their applications in the digital design. The chapter is useful to understand the Moore and Mealy machine designs, encoding methods and their use in the design.

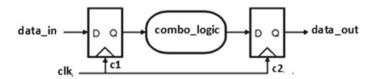

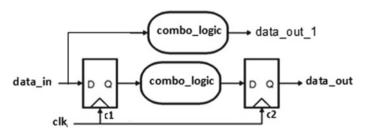

Chapter 10 "Advanced Design Techniques-1" discusses about the data and control path designs and the timing of the synchronous sequential circuits. Even this chapter focuses on the various advanced design techniques which are useful to optimize for the area, speed and power. These techniques we can use in the design of the architecture and also in the high-speed digital designs.

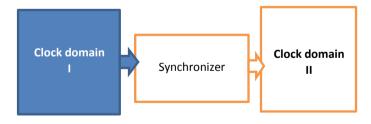

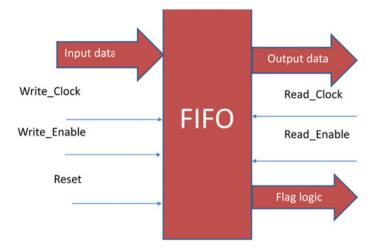

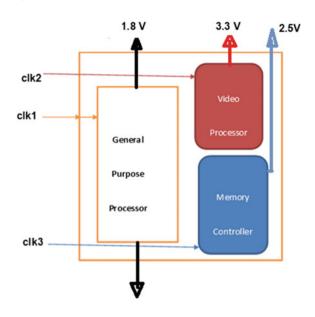

Chapter 11 "Advanced Design Techniques-2" focuses on the architecture design for the given functional specifications. The chapter is even useful to understand about the design specific scenarios like multiple clock domains, multiple power domains, synchronizers, design specific scenarios and the performance improvement for the design.

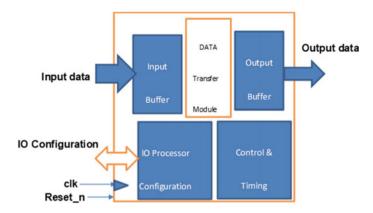

Chapter 12 "System Design and Considerations" discusses about the use of the digital design techniques in the system design, IO and memory interfacing and other important goals

The book includes many practical design scenarios and techniques. The book is useful to understand the design techniques and important design and optimization scenarios. The book even covers the performance improvement strategies and techniques at the logic and architecture level.

This book is useful to the engineering students, digital design engineers, VLSI beginners and professionals those who wish to design the digital systems!

Pune, India Vaibbhav Taraate

### Acknowledgements

Most of the engineers requested me to write a book on *Digital Design Techniques* and *Exercises* during the corporate programs. Over the period of time whatever experience which I have gained I thought to document in this manuscript.

This book is possible due to the help of many people. I am thankful to all the participants to whom I taught the subject "Digital Design in VLSI perspective" in various multinational corporations. I am thankful to all those entrepreneurs, design/verification engineers and managers with whom I worked in the past almost around 20 years.

I am thankful to my dearest friends for their constant support. Especially, I am thankful to my students, friends, well-wishers and my family members. Special thanks to Neeraj, Deepesh, Jyoti, Suman and Annu for their best wishes and valuable help during the manuscript work.

Special thanks to Somi, Siddhesh and Kajal for their faith and belief on me and for their better support during manuscript work. Especially thankful to Ravi, Divya, Swati, Rahul for their best wishes!

Finally, I am thankful to Springer Nature staff, especially Swati Meherishi, Muskan Jaiswal, Ashok Kumar, Silky Sinha for their great support during the various phases of the manuscript.

Special thanks in advance to all the readers and engineers for buying, reading and enjoying this book!

### **Contents**

| Basi | cs of Digit | al Design                                      |

|------|-------------|------------------------------------------------|

| 1.1  |             | Logic and the Evolution                        |

| 1.2  | The Im      | portant Considerations                         |

|      | 1.2.1       | Area of the Design                             |

|      | 1.2.2       | Speed of the Design                            |

|      | 1.2.3       | Power                                          |

| 1.3  | Logic (     | Gates                                          |

| 1.4  | De Mo       | rgan's Theorems                                |

|      | 1.4.1       | NAND is Equal to Bubbled OR                    |

|      | 1.4.2       | NOR is Equal to Bubbled AND                    |

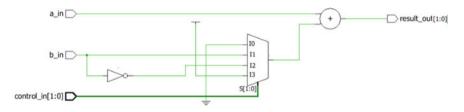

| 1.5  | Multipl     | lexer as Universal Logic                       |

| 1.6  | Optimi      | zation Goals and Applications in VLSI Context  |

| 1.7  | Exercis     | ses                                            |

|      | 1.7.1       | Exercise 1: Use of the Logical Expressions     |

|      |             | to Get the Logic Equivalent                    |

|      | 1.7.2       | Exercise 2: Cascade Logic and How to Get Logic |

|      |             | Expression?                                    |

|      | 1.7.3       | Exercise 3: Complement Logic                   |

|      | 1.7.4       | Exercise 4: Logic Expression for the Cascade   |

|      |             | Logic                                          |

|      | 1.7.5       | Exercise 5: Output Expression for the Cascade  |

|      |             | Logic                                          |

|      | 1.7.6       | Exercise 6: Propagation Delay for the Cascade  |

|      |             | Logic                                          |

|      | 1.7.7       | Exercise 7: Logic Gate Output Expression       |

|      | 1.7.8       | Exercise 8: Propagation Delay for the Cascade  |

|      |             | Logic                                          |

|      | 1.7.9       | Exercise 9: The Equivalent Logic Expression    |

|      | 1.7.10      | Exercise 10: The Equivalent Logic Gate         |

| 1.8  | Importa     | ant Takeaways                                  |

|      |             |                                                |

xii Contents

| Desig | gn Using  | Universal Logic                                 |

|-------|-----------|-------------------------------------------------|

| 2.1   | What I    | s Universal Logic?                              |

| 2.2   | Univer    | rsal Gates                                      |

|       | 2.2.1     | NAND                                            |

|       | 2.2.2     | NOR                                             |

|       | 2.2.3     | Other Application-Specific Universal Gates      |

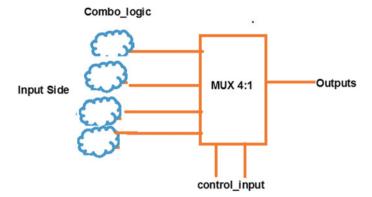

| 2.3   | Multip    | lexers                                          |

|       | 2.3.1     | Design Using 2:1 Mux                            |

|       | 2.3.2     | 4:1 MUX Using 2:1 Mux                           |

|       | 2.3.3     | Design Using Multiplexers                       |

| 2.4   | Exerci    |                                                 |

|       | 2.4.1     | Exercise 1: Design Using Universal Gates        |

|       | 2.4.2     | Exercise 2: Design Using the MUX                |

|       | 2.4.3     | Exercise 3: Design Using MUX                    |

|       | 2.4.4     | Exercise 4: Design Using Custom Gates           |

|       | 2.4.5     | Exercise 5: Optimization Exercise               |

|       | 2.4.6     | Exercise 7: Design Using the MUX                |

|       | 2.4.7     | Exercise 8: Design Using MUX                    |

|       | 2.4.8     | Exercise 9: Design Using Custom Gates           |

| 2.5   |           | eations and Use in VLSI Context                 |

| 2.6   | Import    | ant Takeaways                                   |

| Com   | binationa | al Design Resources                             |

| 3.1   | Code (    | Converters                                      |

|       | 3.1.1     | Three-Bit Binary-to-Gray Code Converter         |

|       | 3.1.2     | 3-Bit Gray-to-Binary Code Converter             |

| 3.2   | Arithm    | netic Resources                                 |

|       | 3.2.1     | Half-Adder                                      |

|       | 3.2.2     | Half-Subtractor                                 |

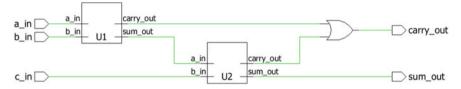

|       | 3.2.3     | Full-Adder                                      |

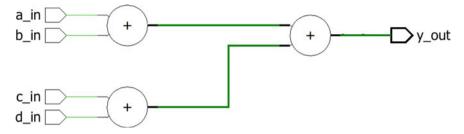

| 3.3   |           | Arithmetic Resources in the Design              |

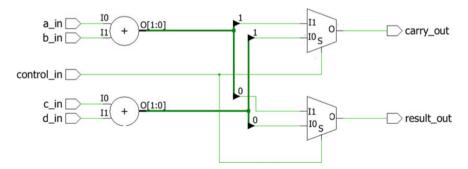

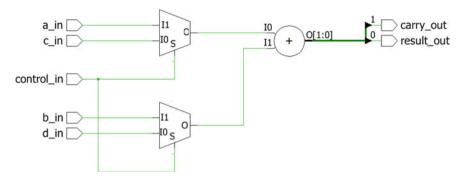

| 3.4   | Design    | Using Arithmetic Resources and Control Elements |

| 3.5   | Optimi    | ization Goals                                   |

| 3.6   | Proces    | sor Logic and Need of Arithmetic Resources      |

| 3.7   | Exerci    |                                                 |

|       | 3.7.1     | Exercise 1: Cascade Versus Parallel Logic       |

|       | 3.7.2     | Exercise 2: Delay of the Design                 |

|       | 3.7.3     | Exercise 3: Speed                               |

|       | 3.7.4     | Exercise 4: Design to perform the Addition      |

|       |           | and Subtraction                                 |

|       | 3.7.5     | Exercise 4: Design with the Goal to Use         |

|       |           | Resource Sharing                                |

| 3.8   | Import    | ant Takeaways                                   |

Contents xiii

| 4 | Case  | Study: ALU Design                                       |

|---|-------|---------------------------------------------------------|

|   | 4.1   | Design Specifications and Their Role                    |

|   | 4.2   | What Is ALU? 6                                          |

|   | 4.3   | Arithmetic Unit Design                                  |

|   |       | 4.3.1 Resources Required 6                              |

|   |       | 4.3.2 How to Start Design of ALU? 6                     |

|   |       | 4.3.3 How to Design the Logic                           |

|   |       | 4.3.4 Exercise 1: Optimization of the Arithmetic Unit 6 |

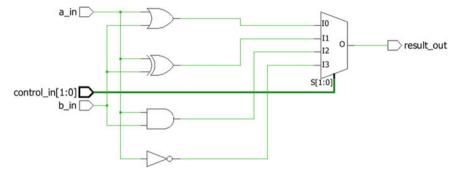

|   |       | 4.3.5 Logic Unit Design 6                               |

|   |       | 4.3.6 Resources Required 6                              |

|   |       | 4.3.7 How to Design the Logic Unit to have Better       |

|   |       | Area? 6                                                 |

|   | 4.4   | ALU Design 6                                            |

|   |       | 4.4.1 Resource Requirement and How to Design            |

|   |       | Efficient ALU? 6                                        |

|   |       | 4.4.2 ALU Design to have Better Area 6                  |

|   |       | 4.4.3 Exercise 2: Optimization of ALU                   |

|   | 4.5   | Few Important Design Guidelines                         |

|   | 4.6   | Important Takeaways 7                                   |

| 5 | Droot | ical Scenarios and the Design Techniques                |

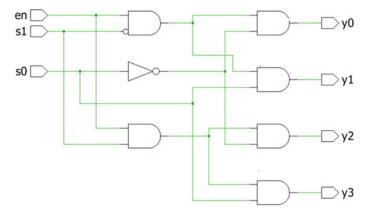

| J | 5.1   | Parallel Logic                                          |

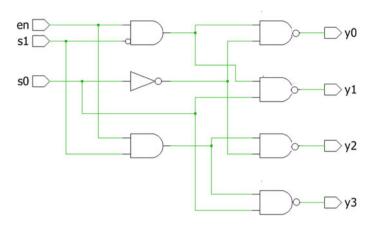

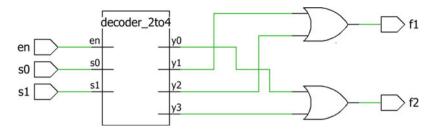

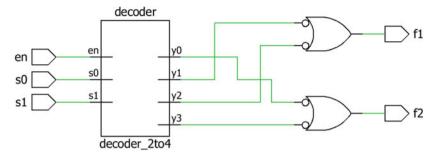

|   | 3.1   | 5.1.1 Decoder 2 to 4                                    |

|   | 5.2   | Encoder                                                 |

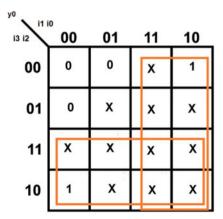

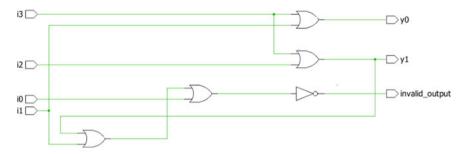

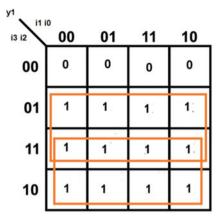

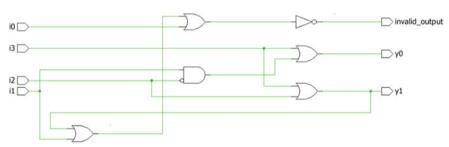

|   | 5.3   | Encoder with Invalid Output Detection Logic 7           |

|   | 5.4   | Exercises                                               |

|   | 3.4   | 5.4.1 Exercise 1: Design of Decoder Having              |

|   |       | Active-Low Output                                       |

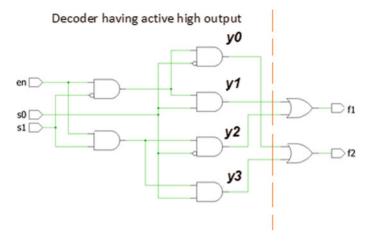

|   |       | 5.4.2 Exercise 2: Design the Function Using Decoder 8   |

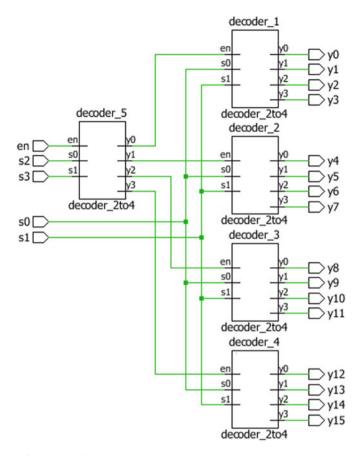

|   |       | 5.4.3 Exercise 3: Design Using Decoders 8               |

|   |       | 5.4.4 Exercise 4: Design Using Decoder and NAND         |

|   |       | Gates                                                   |

|   |       | 5.4.5 Exercise 5: Design Using Decoders 8               |

|   |       | 5.4.6 Exercise 6: Priority Encoder Design               |

|   | 5.5   | Important Takeaways                                     |

|   |       | •                                                       |

| 6 |       | s of the Sequential Design                              |

|   | 6.1   | What Is Sequential Logic Design?                        |

|   | 6.2   | Sequential Design Elements                              |

|   | 6.3   | Level Versus Edge-Triggered Logic                       |

|   | 6.4   | Latches and Their Use in the Design                     |

|   |       | 6.4.1 Positive-Level-Sensitive D Latch 9                |

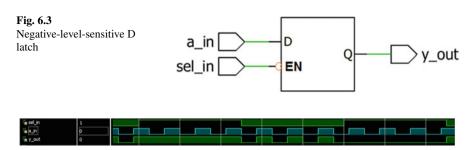

|   |       | 6.4.2 Negative-Level-Sensitive D Latch                  |

|   | 6.5   | Edge-Sensitive Elements and Their Role                  |

|   |       | 6.5.1 Positive Edge-Sensitive D Flip-Flop               |

|   |       | 6.5.2 Negative Edge-Sensitive D Flip-Flop               |

|   | 6.6   | Applications                                            |

xiv Contents

|   |            | 6.6.1    | Applications of the Latches                    | 95  |

|---|------------|----------|------------------------------------------------|-----|

|   |            | 6.6.2    | Applications of the Flip-Flop                  | 96  |

|   | 6.7        | Exerci   | ses                                            | 96  |

|   |            | 6.7.1    | Exercise 1: Design Positive-Level-Sensitive    |     |

|   |            |          | Latch Using Multiplexers                       | 96  |

|   |            | 6.7.2    | Exercise 2: Design Negative-Level-Sensitive    |     |

|   |            |          | Latch Using Multiplexers                       | 97  |

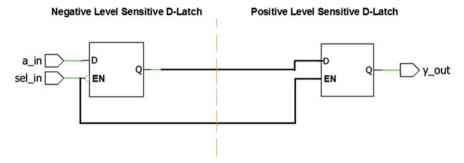

|   |            | 6.7.3    | Exercise 3: What Is the Functionality          |     |

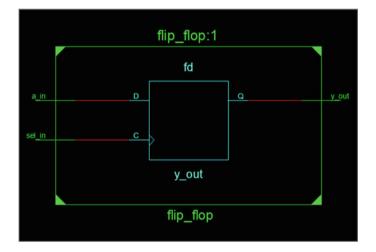

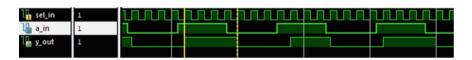

|   |            |          | of the Following Design?                       | 98  |

|   |            | 6.7.4    | Exercise 4: Design the Positive Edge-Sensitive |     |

|   |            |          | Flip-Flop Using Latches                        | 99  |

|   |            | 6.7.5    | Exercise 5: Design the Negative Edge-Sensitive |     |

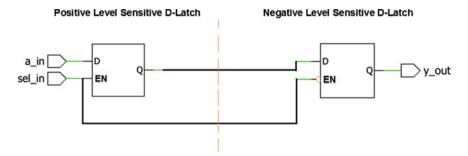

|   |            |          | Flip-Flop Using Latches                        | 100 |

|   |            | 6.7.6    | Exercise 6: What Is the Operating Frequency    |     |

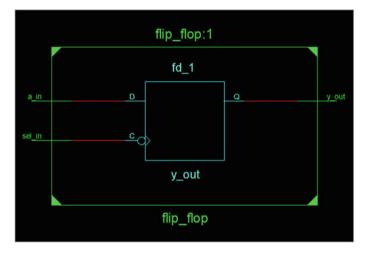

|   |            |          | of the Following Circuit?                      | 101 |

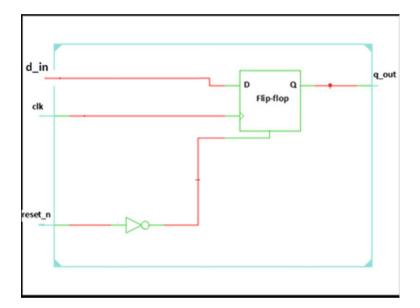

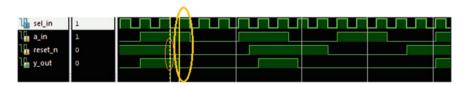

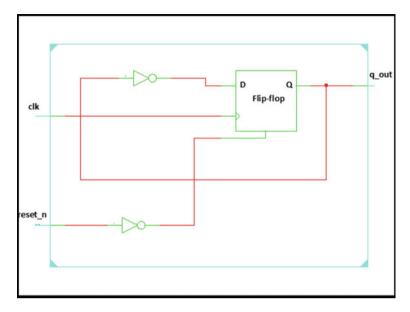

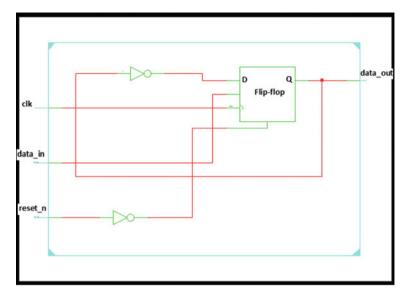

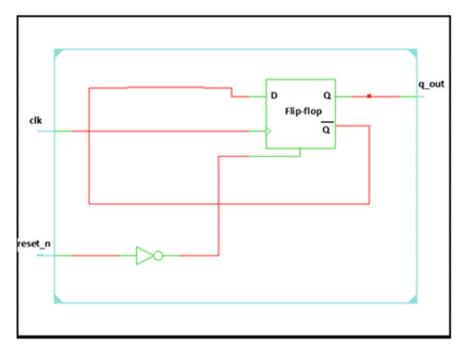

|   |            | 6.7.7    | Exercise 7: The Asynchronous Clear             | 101 |

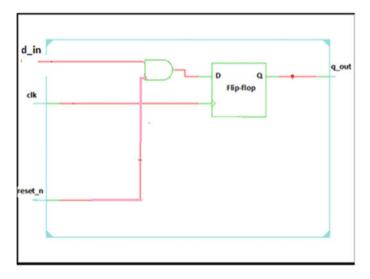

|   |            | 6.7.8    | Exercise 8: The Synchronous Clear              | 102 |

|   | 6.8        | Import   | tant Takeaways                                 | 104 |

| 7 | Soone      | ntial Da | osian Taahniawas                               | 105 |

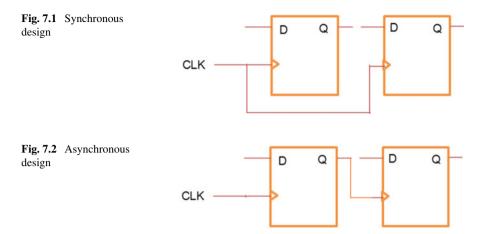

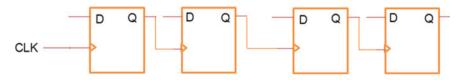

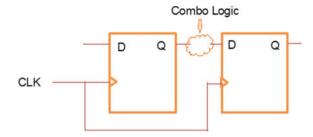

| , | 7.1        |          | ronous Design                                  | 105 |

|   | 7.1        |          | hronous Design                                 | 105 |

|   | 7.2        | •        | o Use Synchronous Design?                      | 103 |

|   | 1.3        | 7.3.1    | Which Elements We Should Use During Design?    | 100 |

|   | 7.4        |          | -Flop and Use in the Design                    | 107 |

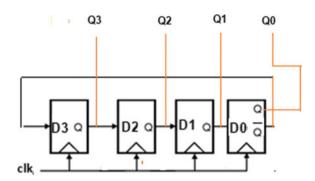

|   | 7.5        | _        | r for the given specifications                 | 110 |

|   | 7.6        |          | of the Synchronous Counters                    | 110 |

|   | 7.0        |          | se 1: Design of the Synchronous Down-Counters  | 111 |

|   | 7.7        |          | se 2: Design of the Synchronous Gray Counter   | 115 |

|   | 7.8<br>7.9 |          | nportant Guidelines                            | 113 |

|   | 7.9        |          | tant Takeaways                                 | 110 |

|   | 7.10       | шрог     | tant Takeaways                                 | 119 |

| 8 | Impo       | rtant De | sign Scenarios                                 | 121 |

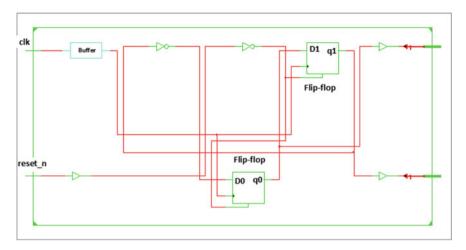

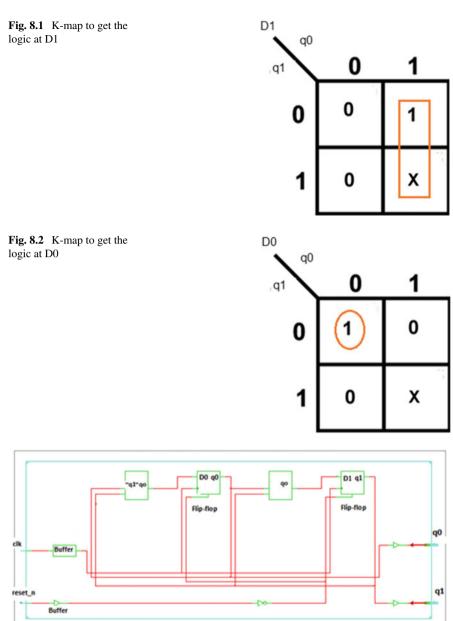

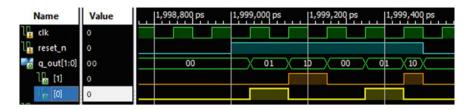

|   | 8.1        | MOD-     | 3 Counter                                      | 121 |

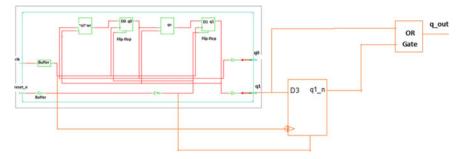

|   | 8.2        | The D    | esign of MOD-3 Counter with 50% Duty Cycle     | 124 |

|   | 8.3        | Applic   | eations and Use of Counters                    | 125 |

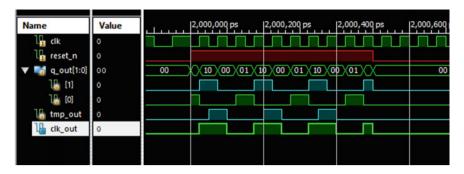

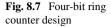

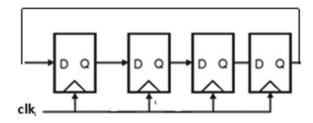

|   |            | 8.3.1    | Ring Counter                                   | 126 |

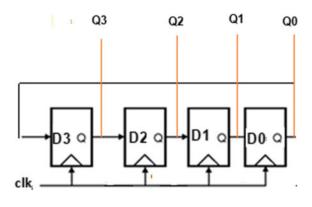

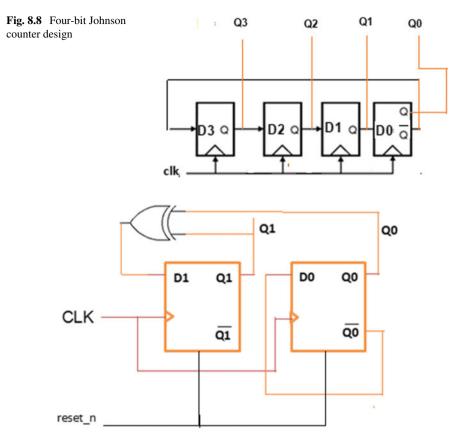

|   |            | 8.3.2    | Johnson Counter                                | 128 |

|   | 8.4        | Exerci   | ses                                            | 130 |

|   |            | 8.4.1    | Exercise 1: The Counter Output                 | 131 |

|   |            | 8.4.2    | Exercise 2: Find the Output Sequence           | 131 |

|   |            | 8.4.3    | Exercise 3: Operating Frequency of Design      | 133 |

|   |            | 8.4.4    | Exercise 4: Output on 1024th Clock Cycle       | 133 |

|   |            | 8.4.5    | Exercise 5: Output on the 4th Clock Cycle      | 133 |

|   |            | 8.4.6    | Exercise 6: Output at 10th Clock Pulse         | 134 |

Contents xv

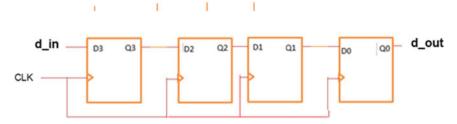

|    |      | 8.4.7     | Exercise 7: Design the Serial Input Serial Output |     |

|----|------|-----------|---------------------------------------------------|-----|

|    |      |           | Shift Register                                    | 136 |

|    | 8.5  | Importa   | nt Takeaways                                      | 136 |

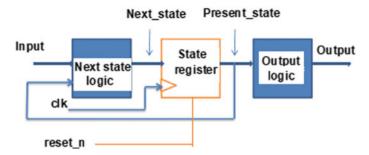

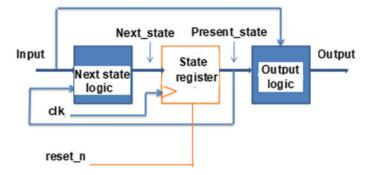

| 9  | FSM  | Design Te | echniques                                         | 137 |

|    | 9.1  | What Is   | FSM?                                              | 137 |

|    |      | 9.1.1     | Moore FSM                                         | 138 |

|    |      | 9.1.2     | Mealy FSM                                         | 138 |

|    |      | 9.1.3     | Moore Versus Mealy FSM                            | 139 |

|    | 9.2  | State Er  | ncoding Methods                                   | 139 |

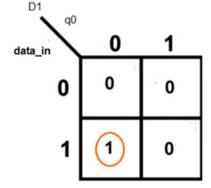

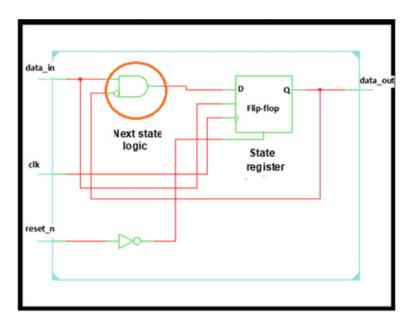

|    | 9.3  | Moore I   | FSM Design                                        | 141 |

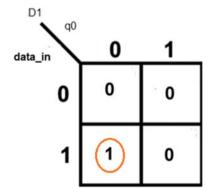

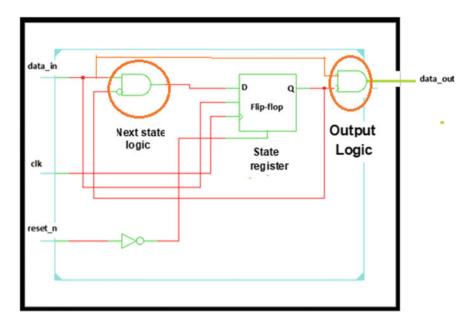

|    | 9.4  | Mealy F   | FSM Design                                        | 144 |

|    | 9.5  | Applica   | tions and Design Strategies                       | 146 |

|    | 9.6  | Exercise  | es                                                | 147 |

|    |      | 9.6.1     | Exercise 1: Moore Machine State Diagram           | 147 |

|    |      | 9.6.2     | Exercise 2: Mealy Machine                         | 148 |

|    |      | 9.6.3     | Exercise 3: One-Hot Encoding                      | 149 |

|    |      | 9.6.4     | Exercise 4: FSM Area and Power Optimization       | 150 |

|    | 9.7  | Importa   | nt Takeaways                                      | 151 |

| 10 | Adva | nced Desi | gn Techniques-1                                   | 153 |

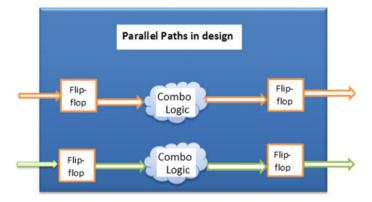

|    | 10.1 |           | Paths in the Design                               | 153 |

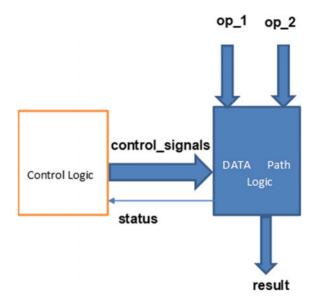

|    | 10.2 | Data an   | d Control Paths                                   | 154 |

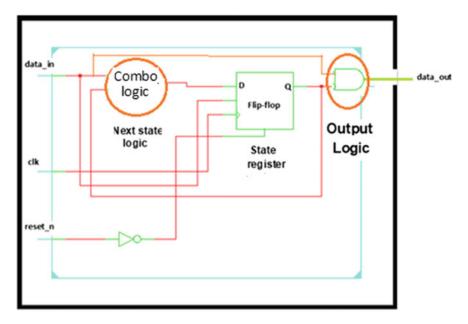

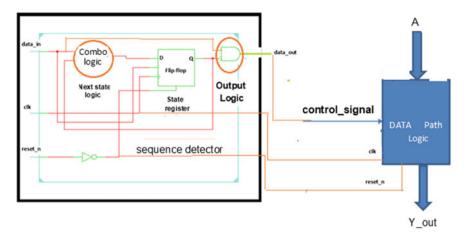

|    | 10.3 | Mealy S   | Sequence Detector Design                          | 155 |

|    | 10.4 |           | d Control Path Design Techniques                  | 159 |

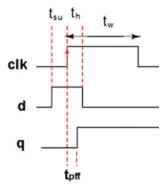

|    | 10.5 | Flip-Flo  | pp Timing Parameters                              | 160 |

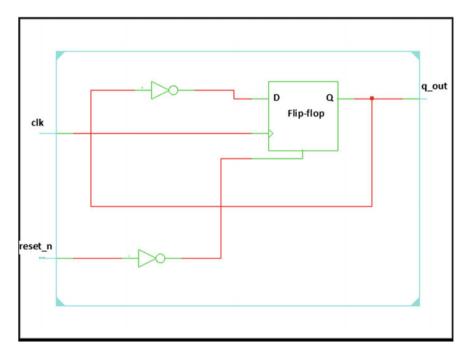

|    | 10.6 | Exampl    | e on Performance Improvement of the Design        | 161 |

|    | 10.7 | Exercise  | es                                                | 163 |

|    |      | 10.7.1    | Exercise 1: Maximum Operating Frequency           | 163 |

|    |      | 10.7.2    | Exercise 2: Timing Paths                          | 164 |

|    |      | 10.7.3    | Exercise 3: Maximum Operating Frequency           | 165 |

|    |      | 10.7.4    | Exercise 4: Positive Clock Skew and Maximum       |     |

|    |      |           | Operating Frequency for the Design                | 165 |

|    |      | 10.7.5    | Exercise 5: Negative Clock Skew and Maximum       |     |

|    |      |           | Operating Frequency for the Design                | 166 |

|    | 10.8 | Importa   | nt Takeaways                                      | 167 |

| 11 | Adva | nced Desi | gn Techniques-2                                   | 169 |

|    | 11.1 | Multiple  | e Clock Domain Designs                            | 169 |

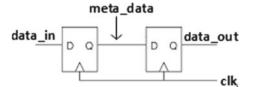

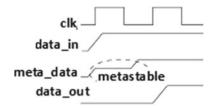

|    | 11.2 |           | bility                                            | 170 |

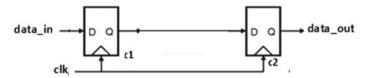

|    | 11.3 |           | Path Synchronizer                                 | 171 |

|    | 11.4 |           | th Synchronizer                                   | 172 |

|    | 11.5 |           | e Power Domain Designs                            | 172 |

|    | 11.6 |           | cture-Level Designs                               | 173 |

|    | 11.7 |           | e Can Improve the Design Performance              | 174 |

|    | 11.8 |           | gital Systems and Design                          | 176 |

xvi Contents

|     | 11.9   | Exercises                                            | 176 |  |

|-----|--------|------------------------------------------------------|-----|--|

|     |        | 11.9.1 Exercise 1: FIFO Depth Calculation            | 177 |  |

|     |        | 11.9.2 Exercise 2: FIFO Depth Calculation            | 177 |  |

|     |        | 11.9.3 Exercise 3: FIFO Depth Calculation            | 178 |  |

|     |        | 11.9.4 Exercise 4: FIFO Depth Calculation            | 179 |  |

|     |        | 11.9.5 Exercise 5: FIFO Depth Calculation            | 179 |  |

|     | 11.10  | Important Takeaways                                  | 180 |  |

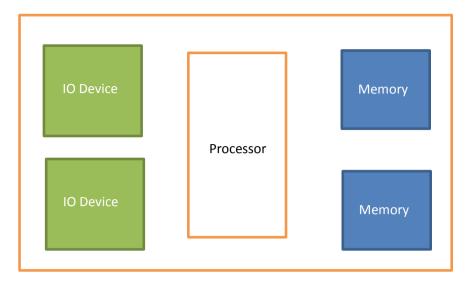

| 12  | Systen | n Design and Considerations                          | 181 |  |

|     | 12.1   | System Design                                        | 181 |  |

|     | 12.2   | What We Need to Think About?                         |     |  |

|     | 12.3   | Important Considerations                             |     |  |

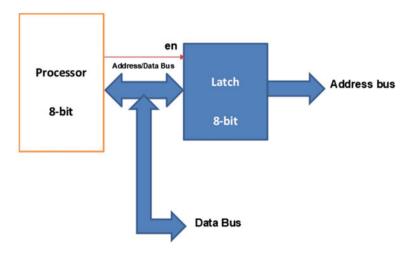

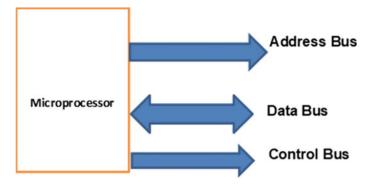

|     | 12.4   | Let Us Understand the Microprocessor Capabilities 18 |     |  |

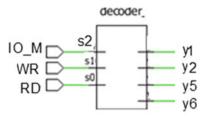

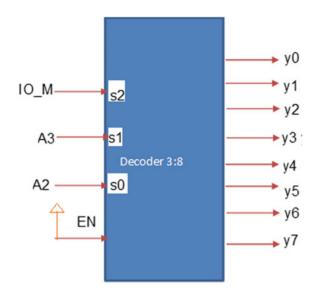

|     | 12.5   | Control Signal Generation Logic                      |     |  |

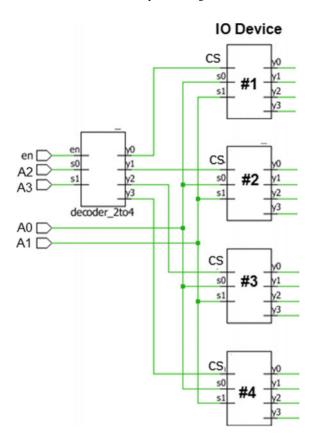

|     | 12.6   | IO Devices and Communication with the Processor      | 186 |  |

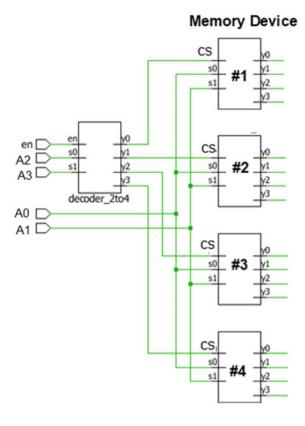

|     | 12.7   | Memory Devices and Communication with the Processor  | 187 |  |

|     | 12.8   | Design Scenarios and Optimization                    |     |  |

|     | 12.9   | Concluding Comments                                  | 190 |  |

|     |        |                                                      |     |  |

| Ind | ex     |                                                      | 193 |  |

### **About the Author**

Vaibbhav Taraate is Entrepreneur and Mentor at "1 Rupee S T". He holds a BE (Electronics) degree from Shivaji University, Kolhapur in 1995 and secured a gold medal for standing first in all engineering branches. He has completed his M.Tech. (Aerospace Control and Guidance) in 1999 from Indian Institute of Technology (IIT) Bombay. He has over 18 years of experience in semi-custom ASIC and FPGA design, primarily using HDL languages such as Verilog and VHDL. He has worked with few multinational corporations as consultant, senior design engineer, and technical manager. His areas of expertise include RTL design using VHDL, RTL design using Verilog, complex FPGA-based design, low power design, synthesis/optimization, static timing analysis, system design using microprocessors, high speed VLSI designs, and architecture design of complex SOCs.

# **Chapter 1 Basics of Digital Design**

1

The basics of digital logic design and the various efficient techniques are useful during the optimization of the combinational logic.

Most of the time, we experience the need of the digital design techniques to design the digital systems. If we consider any digital system, then the understanding of the digital design techniques, and their use is helpful to the engineers to design and implement the systems. The main considerations are the area, speed and power requirements for these systems and their efficient understanding while implementing the digital systems. In this context, the chapter discusses the basics of the digital design techniques with their main important goals.

### 1.1 Digital Logic and the Evolution

The digital logic has evolved during last century and has various efficient techniques. Most of the time, we have used the techniques for the Boolean equation simplifications and for the optimization. The main important techniques are very basic, and they are

- 1. Boolean theorems

- 2. Sum of Product (SOP) and Product of Sum (POS) simplifications

- 3. Karnaugh map (K-map)

- 4. De Morgan's theorems

- 5. Design optimization techniques

- 6. Delay optimization techniques

- 7. Power optimization techniques

- 8. Speed optimization techniques.

Most of us are familiar with these techniques, and we use these during the various design stages such as architecture and micro-architecture of the design.

If we consider the decade of 80s, then we have witnessed migration of EDA tool flow from the schematic entry to the hardware description language (HDL) during 1984–1985. Most of the EDA tool companies evolved the algorithms using the Verilog and VHDL languages to carry out the design and implementation.

Even we have witnessed few PLD-based designs and use of FPGA tools during that decade. In such scenarios, the book is useful to understand various design techniques from basics to complex designs. How to sketch the design architecture and micro-architecture for the design and how to use the advanced digital design techniques is also discussed in this book.

The next few sessions are useful to understand about the basic digital design elements and their role in the design.

### 1.2 The Important Considerations

As most of us are familiar that, the digital design operates on the binary data, we will consider the bit as binary digit, and it has logic 0 and logic 1 values. Logic 0 stands for the VSS (GND) and logic 1 for VDD or VCC. The digital design has classified into the category as follows:

- Combinational logic: In the combinational logic an output is the function of the present input. If input changes, then an output will change after the propagation delay of the combinational logic, hence avoiding the cascading of stages!

Following are examples of the combinational logic:

- a. Logic gates

- b. Arithmetic resources

- c. Multiplexers

- d. Decoders

- e. Demultiplexers

- f. Encoders

- 2. **Sequential logic**: In the sequential design an output is the function of the present input and past output. Examples are latches and flip-flop used to design the sequential logic. The examples of the sequential logic are

- a. Latches

- b. Flip-flops

- c. Counters

- d. Shift registers

- e. Memory elements

While designing the digital logic, the main important considerations are **area**, **speed and power**. Even we need to incorporate the **concurrency**, **parallelism** and the **pipelining** depending on the design goals.

Most of the chapters discuss the use and application of these elements and the design techniques useful to improve the speed, power and area while using these elements!

### 1.2.1 Area of the Design

Area of any design is the number of logic gates or number of logic elements used in the design. The density of logic is how many logic gates in the unit-square area. For example, the processor area is 100,000 logic gates. The design engineers need to use the various design techniques to improve the area of design. Few of the important design techniques are discussed in this book. These techniques are mainly

- 1. Resource sharing

- 2. Logic duplications for FPGA-based designs

- 3. Splitting the larger combinational designs

- 4. Mux-based logic versus gate-based designs

- 5. Resource optimization at the architecture level.

### 1.2.2 Speed of the Design

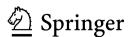

The speed of the design is one of the important parameters, and the speed is limited due to the inertial gate delay or due to cascading of the number of logic stages. As shown in Fig. 1.1 if we consider the CMOS NOT gate then at the output there is formation of the stray capacitance and the inertial delay of the NOT gate is due to the time required for charging and discharging of the capacitor. The inertial delay is

Fig. 1.1 CMOS NOT gate

the propagation delay and defined as the amount of time required for the output to get the valid logic level after change in the input.

For the sequential design, the speed mainly depends upon the timing parameters of the sequential design elements such as setup time, hold time and clock to q delay (propagation delay of the flip-flop). Refer Chap. 10 for more details about the timing parameters.

There are various speed improvement techniques used during the design stages, and few important techniques which are discussed in this book are

- 1. Balancing the register timing

- 2. Pipelining

- 3. Register balancing

- 4. Optimizing for the timing paths in the design

- 5. Use of the parallelism if area is not important consideration.

### 1.2.3 *Power*

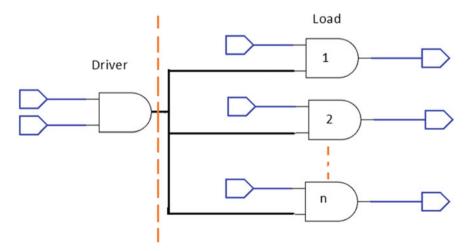

The power is an important design considerations. Most of we have come across the terms such as switching power, static and dynamic power. The power dissipation should be minimum, and the book also focuses on the low power architecture design techniques and their role at various stages of the design. Consider Fig. 1.1, as shown as the stray capacitance is formed at the output, the power is specified as

Power =

$$\alpha C V^2 f$$

where  $\alpha$  = switching factor

C = load or stray capacitance

V =supply voltage and f =frequency

To have the minimum power the load capacitance should be minimum, the voltage should be minimum, but as we cannot compromise on the speed of the design, we need to balance between the desired power and speed of the design.

There is always the trade-off between the speed and power, and the main goal of the logic design team is to have the balance act to achieve the desired speed and power for the design.

There are various power optimization techniques, and few of them are

- 1. Use of low power cells in the design

- 2. Low power aware architecture design

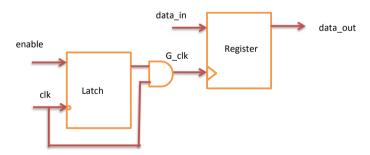

- 3. Clock gating for the sequential logic.

These techniques are discussed in the subsequent chapters.

Now as we have understood the goals and objectives during the logic design and to use the desired techniques, let us start from the basic logic elements. As stated earlier, the basic logic elements are logic gates, and the following section discusses them.

1.3 Logic Gates 5

### 1.3 Logic Gates

The logic gates are important logic design elements. The focus of this book is more on the use of the logic elements to design the area, power and speed-efficient logic. As name indicates that the logic gates are used to perform the desired logic function. The logic gates have inputs and outputs, and they are used to build the combinational and sequential logic.

Although most of the engineers are familiar with the logic gates, let us discuss them in the context of the logic design and optimization of the logic!

### NOT Gate

NOT is complement of the input and also called as logic inverter. It has single input and single output. It just complements the binary input.

The truth table of the NOT gate is shown in Table 1.1. It has input a\_in and an output y\_out. The relationship between the input and output is given by

$$y_out = \overline{a_in}$$

The symbolic representation is shown in Fig. 1.2, and the output is complement of an input. The logic 1 complement is logic 0 and vice versa.

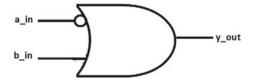

### 2. OR Gate

OR is the logical OR of the inputs and in simple words indicates that this or this! The two input OR gate performs logical OR on the two binary inputs to generate a single bit binary output.

The truth table of the OR gate is shown in Table 1.2. It has inputs a\_in, b-in and an output y\_out. The relationship between the inputs and output is given by

$$y_out = a_in + b_in$$

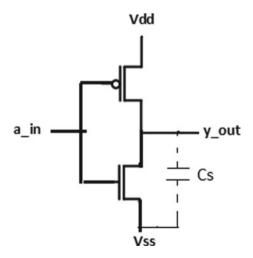

Figure 1.3 is symbolical representation of OR gate, and it indicates that either a\_in or b\_in should be logic 1 to get an output as logic 1. Hence, the logic is OR logic.

**Table 1.1** Truth table of NOT gate

| a_in | y_out |

|------|-------|

| 0    | 1     |

| 1    | 0     |

Fig. 1.2 NOT gate

| <b>Table 1.2</b> Truth table of OR gate | a_in | b_in | y_out |

|-----------------------------------------|------|------|-------|

| guic                                    | 0    | 0    | 0     |

|                                         | 0    | 1    | 1     |

|                                         | 1    | 0    | 1     |

|                                         | 1    | 1    | 1     |

Fig. 1.3 OR gate

### 3. NOR Gate

The NOR is NOT of OR, and the output of NOR gate is logic 1 when all the inputs are logic 0. If one of the input is logic 1, then an output of NOR gate is logic 0. The NOR gate is universal gate because by using the minimum number of NOR gates, any Boolean function can be implemented.

The truth-table of NOR gate is shown in Table 1.3 and has inputs as a\_in, b\_in and output as y\_out. The relationship between the inputs and an output is given by

$$y_out = \overline{a_in + b_in}$$

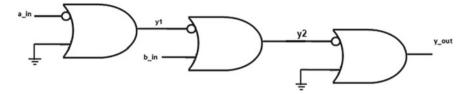

The NOT of OR is shown in Fig. 1.4 which is the cascade of OR and NOT. The issue is the larger propagation delay due to cascading of the OR and NOT. So, during design, avoid the cascade logic. If we consider the delay of each logic gate is 0.5 ns, then the propagation delay of the NOR logic is 1 ns.

**Table 1.3** Truth-table of NOR gate

| a_in | b_in | y_out |

|------|------|-------|

| 0    | 0    | 1     |

| 0    | 1    | 0     |

| 1    | 0    | 0     |

| 1    | 1    | 0     |

Fig. 1.4 NOT of OR

1.3 Logic Gates 7

Fig. 1.5 NOR gate

The symbol of the NOR gate is shown in Fig. 1.5, and the minimum number of NOR gates should be used to implement the Boolean function. By using the minimum number of NOR gates, any Boolean function can be realized, and hence, the NOR gate is called as universal gate.

### 4. AND Gate

The AND logic gate output is logic 1 when both the inputs a\_in and b\_in are at logic 1. Hence, the logic is represented by using a\_in AND b\_in. The logic expression of 2-input AND gate is given by

$$y_out = a_in \cdot b_in$$

The  $\cdot$  (pronounced as dot) indicates the AND operation. The truth-table is shown in Table 1.4. As described in the truth-table when both the inputs a\_in and b\_in are logic 1, an output of the AND gate is logic 1. When one of the input is logic 0, the output of AND gate remains at logic 0.

The symbol of the 2-input AND is shown in Fig. 1.6, and as shown, the AND gate has two inputs a\_in, b\_in and an output as y\_out.

### 5. NAND Gate

NAND is NOT of AND, and the output of NAND is logic 0 when both the inputs are at logic 1. If one of the input of NAND gate is at logic 0, then an output of NAND

**Table 1.4** Truth table of AND gate

| a_in | b_in | y_out |

|------|------|-------|

| 0    | 0    | 0     |

| 0    | 1    | 0     |

| 1    | 0    | 0     |

| 1    | 1    | 1     |

Fig. 1.6 AND gate

| Table 1.5 | Truth table of |

|-----------|----------------|

| NAND gat  | e              |

| a_in | b_in | y_out |

|------|------|-------|

| 0    | 0    | 1     |

| 0    | 1    | 1     |

| 1    | 0    | 1     |

| 1    | 1    | 0     |

Fig. 1.7 NOT of AND

gate is logic 1. The truth-table of 2-input NAND gate is described in Table 1.5. The logic expression is given by

$$y_out = \overline{a_in \cdot b_in}$$

The cascade of the AND, NOT is shown in Fig. 1.7. As discussed earlier, the design engineers should avoid the cascading of the stages.

The NAND gate symbolical representation is shown in Fig. 1.8, and as shown, it has two inputs a\_in, b\_in and an output as y\_out.

### 6. XOR Gate

The XOR gate is also called as exclusive OR. The truth-table of the XOR gate is shown in Table 1.6. As shown, the output of the 2-input XOR gate is logic 1 when both the inputs are not equal. The logic expression of XOR gate is

$$y_out = a_in \oplus b_in$$

Fig. 1.8 NAND gate

**Table 1.6** Truth table of XOR gate

| a_in | b_in | y_out |

|------|------|-------|

| 0    | 0    | 0     |

| 0    | 1    | 1     |

| 1    | 0    | 1     |

| 1    | 1    | 0     |

1.3 Logic Gates 9

Fig. 1.9 XOR gate

The symbol of the XOR gate is shown in Fig. 1.9, and as shown, the 2-input XOR gate has inputs a\_in, b\_in and an output as y\_out.

### 7. XNOR Gate

The XNOR is NOT of XOR. The symbol of the XNOR is  $\odot$  (*pronounced as EXNOR*). The logic expression is given by

$$y_out = a_in \odot b_in$$

The EXNOR or exclusive NOR or XNOR these are few names which we use while implementing the design. The XNOR is cascade of the XOR and NOT and hence called as NOT of XOR. The XNOR using XOR is shown in Fig. 1.10.

The truth-table of the XNOR gate is described in Table 1.7. As described, the output of 2-input XNOR gate is logic 1 when both the inputs are equal.

As discussed earlier, avoid the cascading of the stages as it increases the propagation delay.

The symbol of the XNOR gate is shown in Fig. 1.11, and as shown, the logic has a\_in, b\_in inputs and output as y\_out.

Fig. 1.10 NOT of XOR

**Table 1.7** Truth table of XNOR gate

| a_in | b_in | y_out |

|------|------|-------|

| 0    | 0    | 1     |

| 0    | 1    | 0     |

| 1    | 0    | 0     |

| 1    | 1    | 1     |

Fig. 1.11 XNOR gate

| a_in | a_in | b_in | b_in | y_out |

|------|------|------|------|-------|

| 0    | 1    | 0    | 1    | 1     |

| 0    | 1    | 1    | 0    | 1     |

| 1    | 0    | 0    | 1    | 1     |

| 1    | 0    | 1    | 0    | 0     |

Table 1.8 Truth table of bubbled OR is equal to NAND

Fig. 1.12 Bubbled OR is equal to NAND

### 1.4 De Morgan's Theorems

As we have good understanding of the logic gates now, let us try to understand the important theorems as De Morgan's theorems. For the Boolean simplification, the two important theorems are

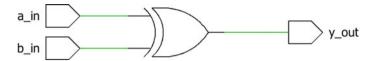

### 1.4.1 NAND is Equal to Bubbled OR

$$\overline{a\_in \cdot b\_in} = \overline{a\_in} + \overline{b\_in}$$

The truth-table is shown in Table 1.8. The output if bubbled OR matches with the output of 2-input NAND, and hence in simple words, we can consider bubbled OR is equal to NAND or vice versa.

For Boolean simplifications, we can use the De Morgan's theorems. We can use the bubbled OR as a NAND during Boolean simplifications (Fig. 1.12).

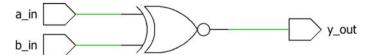

### 1.4.2 NOR is Equal to Bubbled AND

$$\overline{a\_in + b\_in} = \overline{a\_in} \cdot \overline{b\_in}$$

| a_in | a_in | b_in | b_in | y_out |

|------|------|------|------|-------|

| 0    | 1    | 0    | 1    | 1     |

| 0    | 1    | 1    | 0    | 0     |

| 1    | 0    | 0    | 1    | 0     |

| 1    | 0    | 1    | 0    | 0     |

Table 1.9 Truth table of bubbled AND is equal to NOR

Fig. 1.13 Bubbled AND is equal to NOR

The truth-table is shown in Table 1.9. The output if bubbled AND matches with the output of 2-input NOR, and hence in simple words, we can consider bubbled AND is equal to NOR or vice versa.

For Boolean simplifications, we can use the De Morgan's theorems. We can use the bubbled AND as a NOR during Boolean simplifications (Fig. 1.13).

### 1.5 Multiplexer as Universal Logic

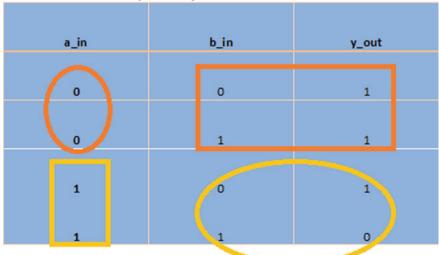

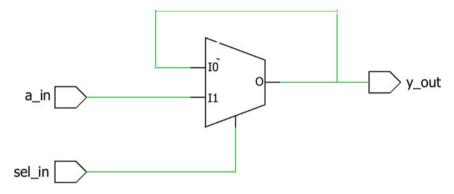

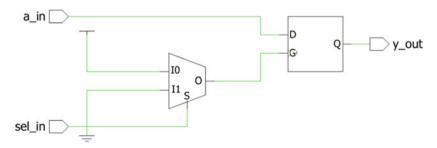

The multiplexer is many to one switch, and they are used in the multiplexing of the buses, clock multiplexing and other various applications. The multiplexer has many inputs and single output. The logic level on the select inputs decides which input is selected, and according to that, the multiplexer output is generated. The multiplexer is also called as mux, and throughout this book, we will call multiplexer as mux. The truth-table of 2:1 mux is shown in Table 1.10. The 2:1 mux has two inputs a\_in, b\_in and single select input sel\_in.

As described, the output of mux is  $b_i$  for sel\_in = 0, for the sel\_in = 1 output is a in.

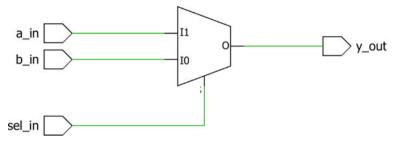

The symbol of the 2:1 mux is shown in Fig. 1.14, and as shown depending on the sel\_in status, it passes one of the input either a\_in, b\_in to an output y\_out.

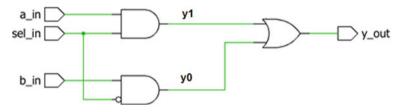

Now, let us implement the 2:1 mux using the logic gates. From the truth table, we can get the product term, and we can use the Sum of Product (SOP) expression to implement the 2:1 mux (Fig. 1.15).

**Table 1.10** Truth table of 2:1 MUX

| sel_in | y_out |

|--------|-------|

| 0      | b_in  |

| 1      | a_in  |

Fig. 1.14 Symbolical representation of 2:1 MUX

Fig. 1.15 Gate-level structure of 2:1 MUX

| sel_in | y_out | Product term                                        |

|--------|-------|-----------------------------------------------------|

| 0      | b_in  | $y0 = \overline{\text{sel\_in}} \cdot \text{b\_in}$ |

| 1      | a_in  | $y1 = sel_in \cdot a_in$                            |

Using the product term, the SOP expression for the 2:1 mux is given by

$$y\_out = y0 + y1$$

$$y\_out = \overline{sel\_in} \cdot b\_in + sel\_in \cdot a\_in$$

### 1.6 Optimization Goals and Applications in VLSI Context

While using the digital elements to design the digital logic, following are few of the optimization goals.

- 1. Do not use the cascading of the logic as it adds significant delays.

- 2. Use the minimum number of universal logic gates to implement the Boolean function.

- 3. Use the multiplexers to implement the Boolean functions.

- 4. Use the low power design cells or gates to improve the power.

- 5. Use the logic cells which has least propagation delay

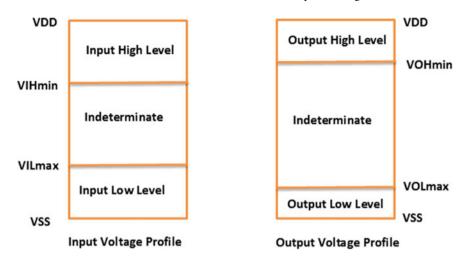

### In the VLSI design context, the following are goals of the designers:

- 1. Understand the compatibility and logic levels of gates.

- 2. Use the minimum number of gates to implement the Boolean function.

- 3. Use the parallel logic if area is not an important parameter.

- 4. Use the low power and high-speed cells during the design.

### 1.7 Exercises

Now let us use the basic fundamentals of the logic gates and let us complete following few exercises.

# 1.7.1 Exercise 1: Use of the Logical Expressions to Get the Logic Equivalent

For the given expression, what is the equivalent logic gate expression at output y?

**Solution**: Given  $y = A + \overline{A} \cdot B$

$$y = (A + \overline{A}) \cdot (A + B)$$

$$y = (A + B)$$

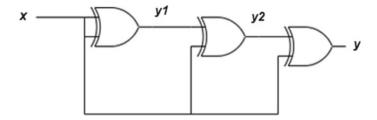

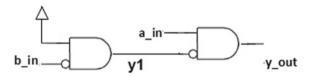

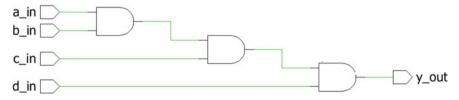

# 1.7.2 Exercise 2: Cascade Logic and How to Get Logic Expression?

For the given cascade logic , what is the equivalent logic gate expression at output y? (Fig. 1.16).

Solution: Output of first XOR gate

$$y1 = X \oplus X = 0$$

Output of second XOR gate

$$y2 = X \oplus 0 = X$$

Fig. 1.16 Cascade XOR gates

Output of third XOR gate

$$y = X \oplus X = 0$$

### 1.7.3 Exercise 3: Complement Logic

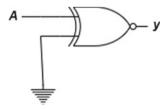

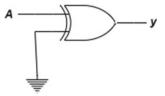

For the given logic gate, what is the equivalent logic expression at output y? (Fig. 1.17).

### **Solution**:

$$y = \overline{A \oplus 0}$$

$$y = \overline{A} \cdot \overline{0} + A \cdot 0$$

$$y = \overline{A} + 0$$

$$y = \overline{A}$$

Fig. 1.17 XNOR gate

1.7 Exercises 15

**Fig. 1.18** Logic realization using NAND

### 1.7.4 Exercise 4: Logic Expression for the Cascade Logic

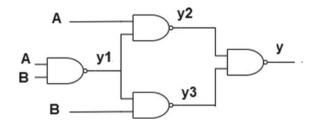

For the given cascade logic , what is the equivalent logic expression at output y? (Fig. 1.18).

**Solution**: Let us find the Boolean equation for y1, y2, y3

$$y1 = \overline{AB}$$

$$y2 = \overline{A \cdot \overline{AB}} = \overline{A \cdot (\overline{A} + \overline{B})} = \overline{A \cdot \overline{B}}$$

$$y3 = \overline{B \cdot \overline{AB}} = \overline{B \cdot (\overline{A} + \overline{B})} = \overline{B \cdot \overline{A}}$$

$$y = \overline{y2 \cdot y3} = \overline{(\overline{A \cdot \overline{B})} \cdot (\overline{B \cdot \overline{A}})}$$

Using De Morgan's theorem that is NAND is equal to bubbled OR, we will get  $y = \overline{(A \cdot \overline{B}) \cdot (\overline{B \cdot \overline{A}})}$

$$y = \overline{(A \cdot \overline{B})} + \overline{(\overline{B} \cdot \overline{A})}$$

$$y = A \cdot \overline{B} + \overline{A} \cdot B$$

### 1.7.5 Exercise 5: Output Expression for the Cascade Logic

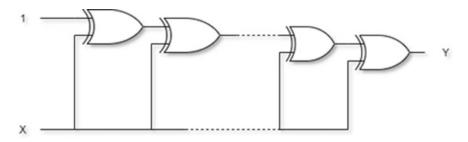

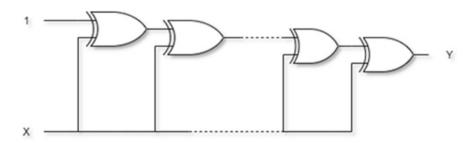

Find the output expression for the cascade logic shown in Fig. 1.19. Consider even number of XOR gates cascaded as shown.

**Solution**: Output of first XOR gate =  $\overline{X}$ Output of second XOR gate =  $\overline{X} \oplus X$

Fig. 1.19 Even number of cascade XOR gates

$$= \overline{X} \cdot \overline{X} \oplus X \cdot X = 1$$

As an even number of XOR gates are connected in cascade, the output of second XOR gate and the last XOR gate are same which is logic 1.

### 1.7.6 Exercise 6: Propagation Delay for the Cascade Logic

Consider the propagation delay of each XOR gate is 0.5 ns and the ten XOR gates are connected in cascade. The propagation delay at the output y of the logic is of how many ns? (Fig. 1.20).

**Solution**: The number of cascade stages are n = 10; each stage has the propagation delay (tpd) of 0.5 ns.

So, the cascade logic has propagation delay of n \* tpd = 10 \* 0.5 ns = 5 ns.

Fig. 1.20 Even gates in cascade

1.7 Exercises 17

Fig. 1.21 XOR gate

### 1.7.7 Exercise 7: Logic Gate Output Expression

For the logic gates shown, what is the equivalent logic expression at output y? (Fig. 1.21).

### **Solution:**

$$y = A \oplus 0$$

$$y = \overline{A} \cdot 0 + A \cdot \overline{0}$$

$$y = 0 + A$$

$$y = A$$

### 1.7.8 Exercise 8: Propagation Delay for the Cascade Logic

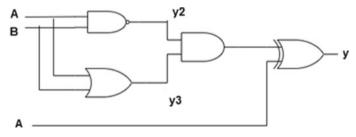

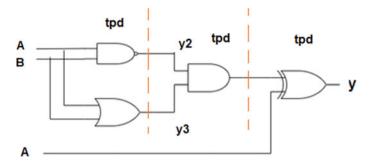

For the following logic, if each gate has propagation delay of 1 ns the maximum propagation delay to get output y is equal to? (Fig. 1.22).

**Solution**: Let us divide the logic shown into three regions as shown in Fig. 1.23.

Fig. 1.22 Logic schematic

Fig. 1.23 Logic regions and delays

As the NAND and OR gate are in parallel the delay is tpd, the delay of AND gate is tpd and XOR gate is tpd, as the gate delay of each gate is 1 ns.

The overall propagation delay to get output y is 3 \* tpd = 3 \* 1 ns = 3 ns.Y

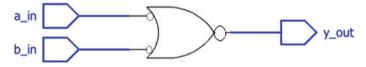

### 1.7.9 Exercise 9: The Equivalent Logic Expression

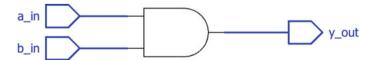

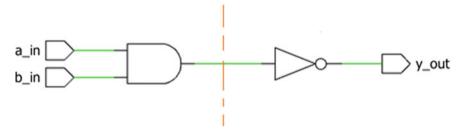

For Fig. 1.24, the equivalent logic gate expression at output y\_out is?

**Solution**: Use the De Morgan's theorem and find the y\_out.

As we know that bubbled OR is NAND

$$\overline{a\_in \cdot b\_in} = \overline{a\_in} + \overline{b\_in}$$

NOT of NAND is AND

$$y_out = \overline{\overline{a_in \cdot b_in}}$$

$$y_out = a_in \cdot b_in$$

So, the above figure logic gate expression is AND logic gate.

Fig. 1.24 Logic gate-1

1.7 Exercises 19

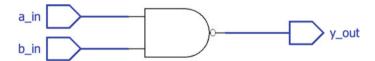

Fig. 1.25 Logic gate-2

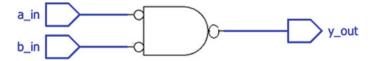

### 1.7.10 Exercise 10: The Equivalent Logic Gate

For Fig. 1.25, the equivalent logic expression at output y\_out is?

**Solution**: Use the De Morgan's theorem and find the y\_out.

As we know that bubbled AND is NOR

$$\overline{a\_in + b\_in} = \overline{a\_in} \cdot \overline{b\_in}$$

NOT of NOR is OR

$$y_out = \overline{\overline{a_in + b_in}}$$

$$y_out = a_in + b_in$$

So, the above figure logic gate is OR gate.

### 1.8 Important Takeaways

Following are few of the important points to conclude this chapter.

- 1. The NAND and NOR are universal logic gates and the goal is to use the minimum number of logic gates to implement the Boolean functions

- 2. NAND logic is equivalent to bubbled OR logic.

- 3. NOR logic is equivalent to the bubbled AND logic.

- Multiplexers are treated as universal logic and used to implement any kind of Boolean function.

- 5. The goal of the system design engineer is to implement the digital system with lesser area, lesser power and more speed.

- 6. Do not use the cascading stages in the design.

# **Chapter 2 Design Using Universal Logic**

The design using universal gates and use of multiplexers as universal logic is useful during the combinational design.

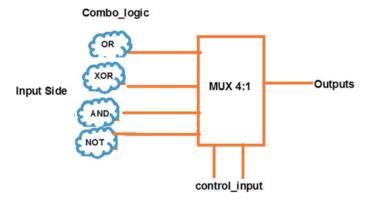

The universal logic gates such as NAND, NOR, MUX and other application-specific or custom gates can be used in the design with the goal of the area optimization. The chapter is useful to understand about the role of these universal logic gates and design by using them! The chapter discusses the cascade and parallel logic and the design techniques to improve the speed of the design and to optimize for the area.

### 2.1 What Is Universal Logic?

Most of us are familiar with the universal logic gates. Mainly, these gates are NAND and NOR. As discussed in the previous chapter, the NAND is bubbled OR and NOR is bubbled AND. The goal of the logic design engineer is to use the minimum number of these gates and to implement the combinational logic which has minimum area. You may feel that it is difficult to directly arrive to the minimum number of the universal gates. But we can use the digital design techniques to get the minimum number!

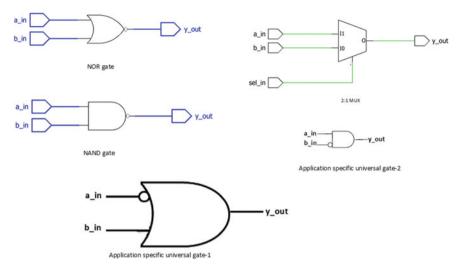

Apart from the NAND and NOR gates, the other universal logic elements are 2:1 mux and the application-specific or custom gates. Figure 2.1 gives information about these gates, and they can be used to implement any combinational logic.

### 2.2 Universal Gates

Most of us are familiar with the universal logic gates as NAND and NOR. These gates are used to design the Boolean functions. The objective of the designer is to use the minimum number of logic gates. The realized logic should have the minimum

Fig. 2.1 Universal gates and mux as a universal logic

area, maximum speed and less power. The section discusses these universal logic gates and design using them.

### 2.2.1 NAND

As discussed in the previous chapter, NAND is NOT of AND. NAND is universal logic gate, and we can use minimum number of NAND gates to implement the Boolean function. Consider the 2-input XOR gate we can use only four NAND gates and can implement the 2-input XOR gate. The relationship between the inputs a\_in, b\_in of NAND gates and an output y\_out is shown in Table 2.1.

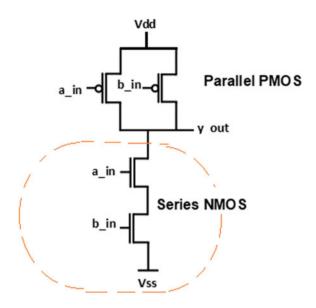

Let us understand the switch-level design of the 2-input NAND gate. As we know that in the CMOS switch-level design we can use PMOS and NMOS. The PMOS passes strong 1 and used in the Vdd section. The NMOS passes the strong 0 and used in the Vss section.

As NAND is NOT of AND, in the lower section we can use the series NMOS switches and as the complement of the NMOS is PMOS, complement of the series

**Table 2.1** Truth-table of 2-input NAND gate

| a_in | b_in | $y\_out = \overline{a\_in \cdot b\_in}$ |

|------|------|-----------------------------------------|

| 0    | 0    | 1                                       |

| 0    | 1    | 1                                       |

| 1    | 0    | 1                                       |

| 1    | 1    | 0                                       |

2.2 Universal Gates 23

**Fig. 2.2** CMOS 2-input NAND

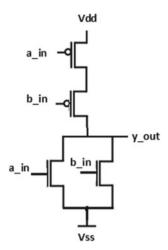

is parallel, in the upper section we can use the parallel connection of the PMOS switches. The upper parallel section uses the supply as Vdd, and the lower series section uses the Vss. Vdd and Vss are complement of each other. The CMOS 2-input NAND gate is shown in Fig. 2.2.

### 2.2.2 NOR

As discussed in the previous chapter, NOR is NOT of OR. NOR is universal logic gate, and we can use minimum number of NOR gates to implement the Boolean function. Consider the 2-input XNOR gate we can use four NOR gates and can implement the 2-input XNOR gate. The relationship between the inputs a\_in, b\_in and an output y\_out is shown in Table 2.2.

Let us understand the switch-level design of the 2-input NOR gate. As NOR is NOT of OR, in the lower section we can use the parallel NMOS switches and as the complement of the NMOS is PMOS, complement of the parallel is series, we can

**Table 2.2** Truth-table of 2-input NOR gate

| a_in | b_in | $y_out = \overline{a_in + b_in}$ |

|------|------|----------------------------------|

| 0    | 0    | 1                                |

| 0    | 1    | 0                                |

| 1    | 0    | 0                                |

| 1    | 1    | 0                                |

**Fig. 2.3** CMOS 2-input NOR gate

use the series connection of the PMOS switches in upper section. The upper series section uses the supply as Vdd, and the lower parallel section uses the Vss. Vdd and Vss are complement of each other. The CMOS 2-input NOR gate is shown in Fig. 2.3.

# 2.2.3 Other Application-Specific Universal Gates

Most of us are familiar with the NAND and NOR as universal gates. We have come across these gates and have habit of using the minimum number of NAND or NOR gates to realize the Boolean function. As discussed in the previous chapter, we can use the minimum number of 2:1 mux to implement the boolean function. The multiplexer is also treated as universal logic.

Apart from the NAND, NOR and 2:1 mux, we can have the other application-specific gates as shown in Figs. 2.4 and 2.6 as the universal logic gates. Thease gates are also used to design the logic function.

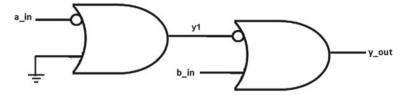

Considering the logic gate shown in Fig. 2.4 if we wish to implement the OR gate using only the minimum number of these types of gates, then we can use following strategy (Fig. 2.5).

**Fig. 2.4** Application-specific universal gate-1

2.2 Universal Gates 25

Fig. 2.5 2-input OR using the application-specific gates

**Fig. 2.6** Application-specific universal gate-2

We can use two application-specific gates in cascade. Let us get the  $y\_out$  expression for Fig.2.5

$$y1 = 0 + \overline{a_{in}}$$

$$y1 = \overline{a_{in}}$$

$$y_{out} = \overline{\overline{a_{in}}} + b_{in}$$

$$y_{out} = a_{in} + b_{in}$$

Consider the logic gate shown in Fig. 2.6 if we wish to implement the AND gate using only the minimum number of these types of gates, then we can use following strategy.

We can use two application-specific gates in cascade (Fig. 2.7).

$$y1 = 1 \cdot \overline{b_{in}}$$

$$y1 = \overline{b_{in}}$$

$$y_{out} = \overline{\overline{b_{in}}} \cdot a_{in}$$

**Fig. 2.7** 2-input AND using the application-specific gates

$$y_out = a_in \cdot b_in$$

### 2.3 Multiplexers

As discussed in the previous chapter, the multiplexers are treated as universal logic. By using the minimum number of multiplexers, any Boolean function can be implemented. The objective of the designer is to have least propagation delay and use of the minimum number of multiplexers. This section is useful to understand the design using minimum number of multiplexers.

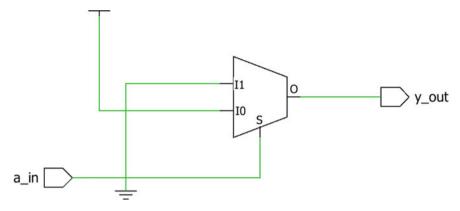

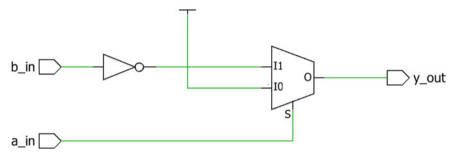

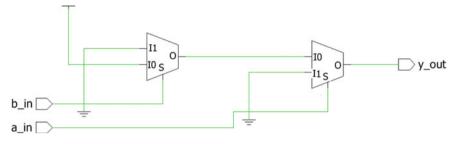

### 2.3.1 Design Using 2:1 Mux

The design using the minimum number of 2:1 mux is discussed in this section. The 2:1 mux is the lowest input multiplexer in the hierarchy. As discussed in the previous chapter, the 2:1 mux has 2-inputs, single select line and single output line. The relationship between the input lines (m) and select lines (n) is given by  $m = 2^n$ .

### **2.3.1.1 NOT Gate Using 2:1 Mux**

Now let us design the NOT gate using 2:1 mux. As shown in the table, the NOT gate has single input and single output.

Now let us compare the truth-table of NOT gate with 2:1 mux.

From comparison of Tables 2.3 and 2.4, it is clear that sel\_in = a\_in, the I0 input should be connected to Vdd (logic 1) and I1 input should be connected to Vss (logic 0). The NOT gate using the single 2:1 mux is shown in Fig. 2.8.

**Table 2.3** Truth-table of NOT gate

| a_in | $y_out = \overline{a_in}$ |

|------|---------------------------|

| 0    | 1                         |

| 1    | 0                         |

**Table 2.4** Truth-table of 2:1 mux

| sel_in | y_out |

|--------|-------|

| 0      | I0    |

| 1      | I1    |

2.3 Multiplexers 27

Fig. 2.8 NOT gate using 2:1 MUX

### 2.3.1.2 OR Gate Using 2:1 Mux

Let us design the OR gate using minimum number of 2:1 mux. Let us think, how many 2:1 mux needed to implement the OR gate? The answer is not very straight forward, and we can arrive to the implementation of OR using 2:1 mux by just observing and rearranging the truth-table of OR. So let us try to do that! (Table 2.5).

Now the better strategy is to divide the table into group of two entries as a\_in is logic 0 for first two entries and logic 1 for next two entries. Now compare the b\_in entries with the y\_out output of OR gate. Using this strategy, let us document the entries so that we can get the equivalent truth table (Table 2.6).

The 2-input OR implementation using the single 2:1 mux is shown in Fig. 2.9. As shown when a\_in which is select line of 2:1 mux is logic 1, an output of 2:1 mux is logic 1. For select line a\_in = 0, an output is b\_in.

Table 2.5 OR gate truth-table

**Table 2.6** 2-input OR using the single 2:1 mux

| sel_in = a_in | y_out |  |

|---------------|-------|--|

| 0             | b_in  |  |

| 1             | 1     |  |

Fig. 2.9 OR gate using 2:1 MUX

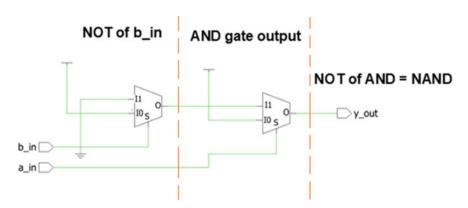

# 2.3.1.3 NAND Using Mux

Now let us use the strategy explained in the above section to implement the 2-input NAND using minimum number of 2:1 multiplexers. Table 2.7 has four entries, and

Table 2.7 Truth-table of 2-input NAND gate

2.3 Multiplexers 29

these are divided into two groups. For first two entries that is  $a_i = 0$  if we compare  $b_i$  with  $y_i$  out, then we are getting an output  $y_i$  out i = 1. For the next two entries if we compare  $b_i$  in with  $y_i$  out of NAND, then we get  $y_i$  out i = 1.

Now most of the time, the beginners conclude that to implement the 2-input NAND gate, we need to have single 2:1 mux (Fig. 2.10) but that is not correct as the logic is not efficient. As shown in Table 2.8 for the select input  $a_i = 1$ , an output  $y_i = b_i = 1$ . So, to implement the NOT of  $b_i = 1$ , we need to have one more multiplexer.

The implementation of 2-input NAND using minimum number of 2:1 mux is shown in Fig. 2.11.

Fig. 2.10 NAND using MUX and NOT

**Table 2.8** 2-input NAND using multiplexer truth-table

| sel_in = a_in | y_out |

|---------------|-------|

| 0             | 1     |

| 1             | b_in  |

Fig. 2.11 NAND using only multiplexers

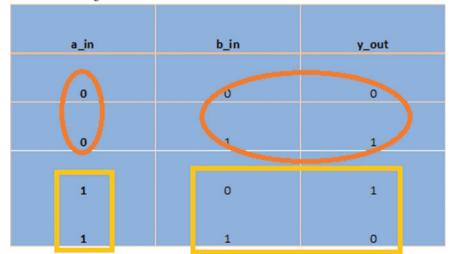

| a_in | b_in | y_out |  |

|------|------|-------|--|

| 0    | 0    | 1     |  |

| 0    | 1    | 0     |  |

| 1    | 0    | 0     |  |

| 1    | 1    | 0     |  |

Table 2.9 Truth-table of 2-input NOR gate

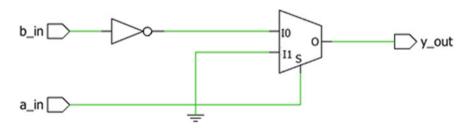

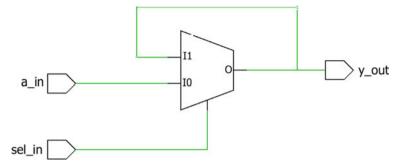

### 2.3.1.4 NOR Using 2:1 Mux

Now let us use the strategy explained in the above section to implement the 2-input NOR using minimum number of 2:1 multiplexers. Table 2.9 has four entries, and these entries are divided into two groups. For first two entries that is  $\underline{a}_{in} = 0$  if we compare  $\underline{b}_{in}$  with  $\underline{y}_{out}$ , then we are getting an output  $\underline{y}_{out} = \underline{b}_{in}$ . For the next two entries if we compare  $\underline{b}_{in}$  with  $\underline{y}_{out}$  of NAND, then we get  $\underline{y}_{out} = 0$ .

To implement the 2-input NOR gate, we need to have single 2:1 mux and NOT gate (Fig. 2.12) but that is not correct approach as our objective is to implement the 2-input NOR using only minimum number of 2:1 mux. As shown in Table 2.9 for the select input  $a_i = 0$ , an output y-out  $= \overline{b_i}$  in. So, to implement the NOT of  $b_i$  in, we need to have one more 2:1 multiplexer (Table 2.10).

The implementation of 2-input NOR using only minimum number of 2:1 mux is shown in Fig. 2.13.

Fig. 2.12 NOR using NOT and 2:1 MUX

2.3 Multiplexers 31

**Table 2.10** 2-input NOR table entries

| sel_in = a_in | y_out |  |

|---------------|-------|--|

| 0             | b_in  |  |

| 1             | 0     |  |

Fig. 2.13 NOR using multiplexers

**Table 2.11** Truth-table of 4:1 mux

| sel_in[1] | sel_in[0] | y_out |

|-----------|-----------|-------|

| 0         | 0         | a_in  |

| 0         | 1         | b_in  |

| 1         | 0         | c_in  |

| 1         | 1         | d_in  |

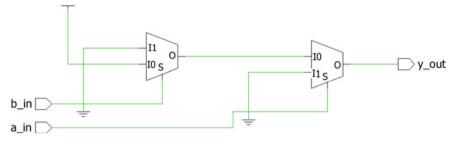

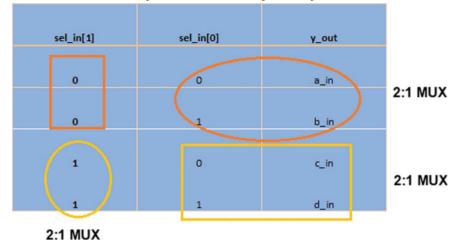

# 2.3.2 4:1 MUX Using 2:1 Mux

The 4:1 mux (Table 2.11) has two select inputs sel\_in[1], sel\_in[0], and depending on the status of the select inputs, one of the output a\_in, b\_in, c\_in, d\_in is connected to an output y\_out. Let us use the minimum number of 2:1 mux to implement the 4:1 mux.

To realize the 4:1 mux using minimum number of 2:1 mux, let us partition the 4:1 mux table into multiple sections as shown in Table 2.12. From the partition, it is clear that we need to have three 2:1 mux to implement the 4:1 mux.

Let us now document the entries (Table 2.13) as shown below to get the output of 4:1 multiplexer (Fig. 2.14).

# 2.3.3 Design Using Multiplexers

So as discussed in the previous few sections, we can use the minimum number of 2:1 mux during the design and realization of the Boolean function. In the practical scenarios, we can use the minimum number of multiplexers to implement the

**Table 2.12** Truth-table to implement the 4:1 mux using 2:1 multiplexers

**Table 2.13** Output mux entries

| sel_in[1] | y_out |

|-----------|-------|

| 0         | y1    |

| 1         | y2    |

Fig. 2.14 4:1 MUX using only 2:1 multiplexers

- Boolean function that is SOP functions

- Clock muxing

- Address data bus multiplexing

- Implementation of the code converters like gray to binary and binary to gray

- Pin multiplexing

2.3 Multiplexers 33

The objective of the logic designer is to use the minimum number of 2:1 mux. Even the cascade multiplexer stages reduce the speed due to increase in propagation delay.

For the better understanding and better design practice, let us discuss few exercises on the universal logic and multiplexer-based designs.

### 2.4 Exercises

Now let us use the understanding on the universal logic gates and the De Morgan's theorem, and let us complete the exercises with the goal of the area optimization.

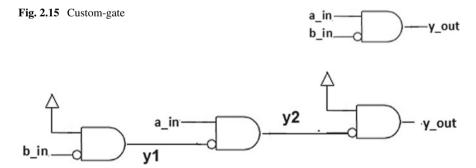

### 2.4.1 Exercise 1: Design Using Universal Gates

Using the following custom gate, design the 2-input NAND gate (Fig. 2.15).

**Solution**: Let us use the understanding on the universal logic gates, and by using the minimum number of these gates, let us design the 2-input NAND gate.

**As NOT of AND is NAND**. Let us implement the AND and then NOT of AND (Fig. 2.16).

$$y1 = 1 \cdot \overline{b_{in}}$$

$$y1 = \overline{b_{in}}$$

$$y2 = \overline{\overline{b_{in}}} \cdot a_{in}$$

Fig. 2.16 2-input NAND using custom gate

$$y2 = a_in \cdot b_in$$

$$y_out = 1 \cdot \overline{y2}$$

$$y_out = \overline{a_in \cdot b_in}$$

Now as by using the above custom gate, we can implement the NAND which is universal gate, and we can treat this custom logic gate as universal gate.

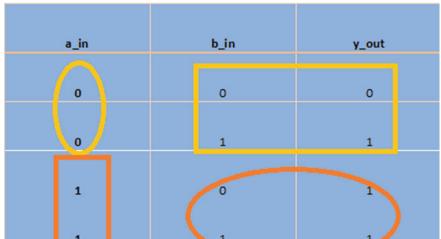

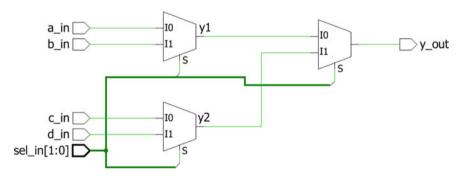

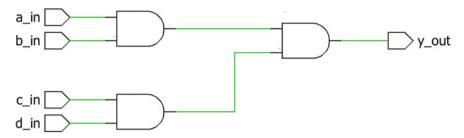

### 2.4.2 Exercise 2: Design Using the MUX

Using the minimum number of 2:1 multiplexers, design the XOR gate.

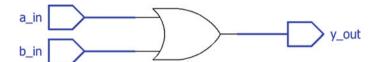

**Solution**: Now the better strategy is to use the truth table of XOR gate (Table 2.14). As shown, the number of entries is 4, and as a\_in = 0 for first two entries and a\_in = 1 for next two entries to realize XOR using the minimum number of 2:1 mux, let us compare b\_in with y\_out of XOR gate.

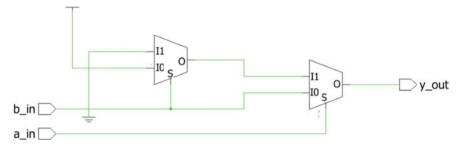

As shown (Table 2.15), for  $a_in = 0$ ,  $y_out = b_in$  and for  $a_in = 1$ ,  $y_out = b_in$ .

The XOR logic using two 2:1 multiplexers is shown in Fig. 2.17.

Table 2.14 XOR gate truth-table

2.4 Exercises 35

Table 2.15

Truth-table for realization of the XOR gate

| a_in | y_out       |

|------|-------------|

| 0    | b_in        |

| 1    | <u>b_in</u> |

Fig. 2.17 XOR gate using 2:1 MUX

# 2.4.3 Exercise 3: Design Using MUX

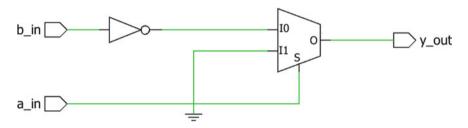

Using the minimum number of 2:1 multiplexers, design the XNOR gate.

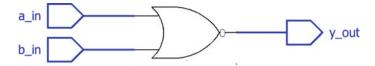

**Solution**: Now the better strategy is to use the truth table of XNOR gate (Table 2.16). As shown, the number of entries is 4 and as a\_in = 0 for first two entries, and a\_in = 1 for next two entries to realize XNOR using the minimum number of 2:1 mux, let us compare b\_in with y\_out of XNOR gate.

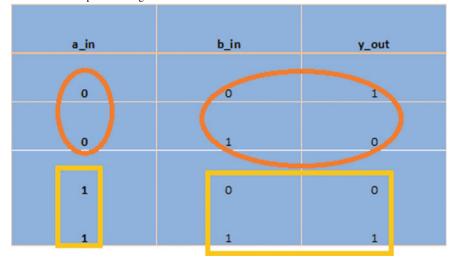

Table 2.16 2-input XNOR gate

**Table 2.17** XNOR entries to realize logic using multiplexers

| a_in | y_out |

|------|-------|

| 0    | b_in  |

| 1    | b_in  |

Fig. 2.18 XNOR gate using 2:1 multiplexers

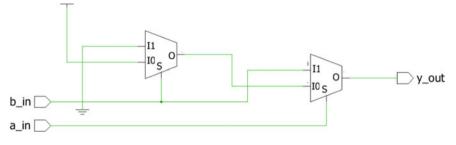

As shown (Table 2.17), for  $\mathbf{a}_{\underline{\mathbf{i}}\mathbf{n}} = \mathbf{0}$ ,  $\mathbf{y}_{\underline{\mathbf{o}}\mathbf{u}\mathbf{t}} = \overline{\mathbf{b}_{\underline{\mathbf{i}}\mathbf{n}}}$  and for  $\mathbf{a}_{\underline{\mathbf{i}}\mathbf{n}} = \mathbf{1}$ ,  $\mathbf{y}_{\underline{\mathbf{o}}\mathbf{u}\mathbf{t}} = \mathbf{b}_{\underline{\mathbf{i}}\mathbf{n}}$ .

The XNOR logic using two 2:1 multiplexers is shown in Fig. 2.18.

# 2.4.4 Exercise 4: Design Using Custom Gates

Using the following custom gate, design the 2-input NOR gate (Fig. 2.19).

**Solution**: Let us use the understanding on the universal logic gates, and by using the minimum number of these gates, let us design the 2-input NOR gate.

As NOT of OR is NOR. Let us implement the OR and then NOT of OR (Fig. 2.20).

$$y1 = 0 + \overline{a_{in}}$$

$$y1 = \overline{a_{in}}$$

$$y2 = \overline{\overline{a_{in}}} + b_{in}$$

Fig. 2.19 Custom gate

2.4 Exercises 37

Fig. 2.20 2-input OR using the application-specific gates

$$y2 = a_in + b_in$$

$$y_out = \overline{a_in + b_in}$$

Now as by using the above custom gate, we can implement the NOR which is universal gate, we can treat this custom logic as universal gate.

## 2.4.5 Exercise 5: Optimization Exercise

Using the minimum number of 2:1 multiplexers, design the NOR gate.

**Solution**: Now the better strategy is to use the truth table of NOR gate (Table 2.18). As shown, the number of entries is 4, and as a\_in = 0 for first two entries and a\_in = 1 for next two entries to realize NOR using the minimum number of 2:1 mux, let us compare b\_in with y\_out of NOR gate.

As shown (Table 2.19), for  $a_in = 0$ ,  $y_out = \overline{b_in}$  and for  $a_in = 1$ ,  $y_out = 0$ .

| a_in |   | b_in |   | y_out |   |  |

|------|---|------|---|-------|---|--|

|      | 0 |      | 0 |       | 1 |  |

|      | 0 |      | 1 |       | 0 |  |

|      | 1 |      | 0 |       | 0 |  |

|      | 1 |      | 1 |       | 0 |  |

Table 2.18 Truth-table of NOR gate

**Table 2.19** NOR to realize using 2:1 mux

| a_in | y_out |

|------|-------|

| 0    | b_in  |

| 1    | 0     |

Fig. 2.21 2-input NOR using only 2:1 multiplexers

Fig. 2.22 NOR using NOT and 2:1 MUX

The NOR logic using two 2:1 multiplexers is shown in Fig. 2.21.

The input multiplexer to get complement of the b\_in can be optimized using the NOT gate. Hence to implement the 2-input NOR (Fig. 2.22), we need to have single 2:1 mux and NOT gate.

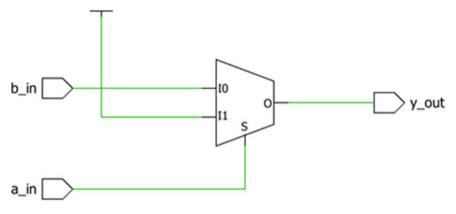

# 2.4.6 Exercise 7: Design Using the MUX

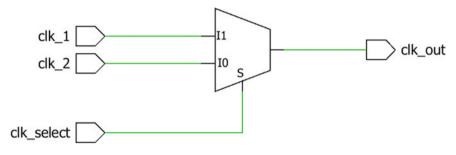

Using the minimum number of 2:1 multiplexers, design the clock muxing. Consider for the clk\_select = 1 output should be clk\_1 and for clk\_select = 0 output should be clk\_2.

**Solution**: Now as only two clock inputs, let us tabulate the specification (Table 2.20). As shown, the number of entries is 2 and as  $clk_select = 0$  the  $y_out = clk_2$ . For  $clk_select = 1$ , the  $y_out = clk_1$ .

Now use the select line  $s = clk\_select$  and inputs as  $I1 = clk\_1$ ,  $I0 = clk\_2$  to get  $clk\_out$  from single 2:1 mux. The design is shown in Fig. 2.23.

2.4 Exercises 39

| Table | 2.20 | Clock | muxing |

|-------|------|-------|--------|

| Table | 4.40 | CIOCK | muamig |

| clk_select | y_out |

|------------|-------|

| 0          | clk_2 |

| 1          | clk_1 |

Fig. 2.23 Clock muxing

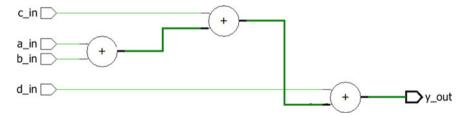

## 2.4.7 Exercise 8: Design Using MUX

Using the minimum number of suitable multiplexer, design the following SOP function.

$$f(\text{sel\_in}[1], \text{sel\_in}[0]) = \sum m(1, 2)$$

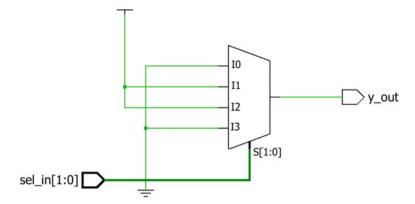

**Solution**: As given, the Boolean function is Sum of Product (SOP) (Table 2.21). As shown, the number of entries is 4, and output f is equal to logic 1 for min terms that is 1, 2. For other combinations, that is for decimal input 0 and 3 output is logic 0.

This can be implemented using pull up (Vdd) or pull down (Vss) at inputs of single 4:1 mux (Fig. 2.24). The select lines of the multiplexer are sel\_in[1], sel\_in[0], and output is y\_out. The inputs I0 = 0, I1 = 1, I2 = 1 and I3 = 0.

Use the strategy in the Exercise 2 to implement using minimum number of 2:1 multiplexers.

**Table 2.21** Truth-table for the given function

| sel_in[1] | sel_in[0] | $f = y_out$ |

|-----------|-----------|-------------|

| 0         | 0         | 0           |

| 0         | 1         | 1           |

| 1         | 0         | 1           |

| 1         | 1         | 0           |

Fig. 2.24 XOR using 4:1 MUX

# 2.4.8 Exercise 9: Design Using Custom Gates

Using the minimum number of suitable multiplexer, design the following SOP function.

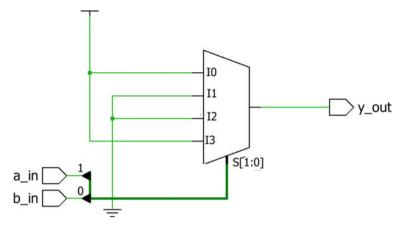

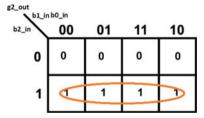

$$f(\text{sel\_in}[1], \text{sel\_in}[0]) = \sum m(0, 3)$$

**Solution**: As given, the Boolean function is Sum of Product (SOP) (Table 2.22). As shown, the number of entries is 4, and output f is equal to logic 1 for min terms that is 0, 3. For other combinations, that is 1 and 2 output is logic 0.

This can be implemented using pull up (Vdd) or pull down (Vss) at inputs of single 4:1 mux (Fig. 2.25). The select lines of the multiplexer are sel\_in[1], sel\_in[0], and output is y\_out. The inputs should be I0 = 1, I1 = 0, I2 = 0 and I3 = 1.

Use the strategy in the Exercise 2 to implement the design using minimum number of 2:1 multiplexers.

**Table 2.22** Truth-table for the given function

| sel_in[1]=a_in | sel_in[0]=b_in | $f = y_out$ |

|----------------|----------------|-------------|

| 0              | 0              | 1           |

| 0              | 1              | 0           |

| 1              | 0              | 0           |

| 1              | 1              | 1           |

Fig. 2.25 XNOR using 2:1 MUX

## 2.5 Applications and Use in VLSI Context

Following are the applications of the mux-based logic and universal logic gates in the VLSI context.

### In the VLSI design context, the following are goals of the designers:

- 1. Understand the Boolean function to be realized and have strategy in place to use the minimum logic gates.

- 2. Use the minimum number of universal logic gates to implement the combinational logic.

- 3. Use the minimum number of multiplexers and try to avoid the cascade stages.

- 4. While implementing the design using multiplexers, avoid the use of the priority logic. Use the mux based logic for pin multiplexing and combinational logic realization.

# 2.6 Important Takeaways

Following are few of the important points to conclude this chapter:

- 1. NAND and NOR are universal logic gates.

- Using 2-input four NAND gates, 2-input XOR gate is realized and uses only 4 NAND gates.

- 3. The minimum number of 2-input NOR gates required to realize the 2-input XNOR gate is 4.

- 4. Multiplexers are used to realize the Boolean functions.

- 5. The minimum number of 2:1 mux required to realize the XOR, XNOR, NOR and NAND gates is equal to 2.

- 6. Only single 2:1 MUX is required to realize the NOT, OR, AND gate.

- 7. Multiplexers are used in the pin muxing and clock muxing.

# **Chapter 3 Combinational Design Resources**

Various combinational resources and the design techniques are useful to design the arithmetic and other processing logic.

The chapter discusses the various code converters, combinational design resources and the arithmetic resources. The design techniques discussed in this chapter are useful to design the combinational or glue logic. The chapter even focuses on the various performance improvement techniques and their use to design the combinational logic.

### 3.1 Code Converters

Most of us are familiar with the various code converters those are useful in the design. Most of the time, we use the binary-to-gray and gray-to-binary code converters. As in the two successive gray codes, only one bit changes; these codes are used to improve the overall power for the design. The main application is use of these code converters in the multiple clock domain and in the FSM designs. Due to lower toggling rate, they are useful to improve the overall power for the design.

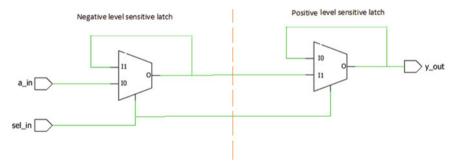

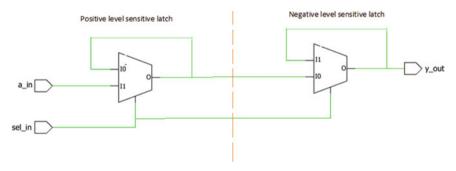

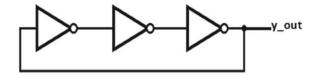

# 3.1.1 Three-Bit Binary-to-Gray Code Converter