Natividad Martínez Madrid Ralf E.D. Seepold *Editors*

## Intelligent Technical Systems

Intelligent Technical Systems

For further volumes: http://www.springer.com/series/7818 Natividad Martínez Madrid · Ralf E.D. Seepold Editors

# Intelligent Technical Systems

*Editors* Prof. Dr. Natividad Martínez Madrid Universidad Carlos III Madrid Depto. Ingenieria Avenida Universidad, 30 28911 Leganes Spain nati@it.uc3m.es

Prof. Dr. Ralf E.D. Seepold Universidad Carlos III Madrid Depto. Ingenieria Avenida Universidad, 30 28911 Leganes Spain ralf@it.uc3m.es

ISBN 978-1-4020-9822-2

e-ISBN 978-1-4020-9823-9

DOI 10.1007/978-1-4020-9823-9

Library of Congress Control Number: 2009920106

© Springer Science+Business Media B.V. 2009

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed on acid-free paper

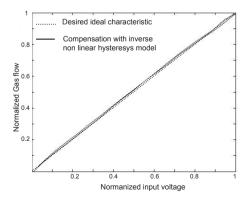

9 8 7 6 5 4 3 2 1

springer.com

## Preface

Intelligent Technical Systems are electronic devices in which one or more networked components are located. Nowadays, the sectors of automotive, medical/e-Health or multimedia show interesting developments. Other wellknown sectors like home or building automation also introduce new concepts in this area.

Intelligent Technical Systems are characterized by a strong interaction with their environment. Several of these systems require mobility support. For example, systems with ubiquitous computing capabilities require a complex design of different interfaces. The integration of human-machine interfaces needs to be considered in special purpose systems, like devices for dependent people with specific needs.

The book *Intelligent Technical Systems* provides an overview on several related fields of applied research, like multimedia systems, embedded programming, middleware platforms, sensor networks/autonomous systems and applications for intelligent engineering. Each area is covered by a separate part of the book.

This book supports application engineers and researchers to get introduced into the topic of Intelligent Technical Systems with the help of concrete examples covering the design and implementation phase.

Madrid, Spain December 2008 Natividad Martínez Madrid Ralf E.D. Seepold

## Contents

| I.  | Multimedia Systems                                                                                                                                        | 1  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.  | Smart Wireless Image Sensors for Video Surveillance<br>Massimo Conti and Simone Orcioni                                                                   | 3  |

| 2.  | Policy Management Architecture for Multimedia<br>Services in a Multi-Provider Scenario<br>Mario Ibáñez, Natividad Martínez Madrid and Ralf Seepold        | 17 |

| 3.  | Embedding Multi-Task Address-Event-Representation<br>Computation<br>Carlos Luján-Martínez, Alejandro Linares-Barranco,<br>Gabriel Jiménez and Antón Civit | 31 |

| 4.  | End to End UPnP AudioVisual Service Provisioning<br>and Management<br>Javier Martínez, Natividad Martínez Madrid and<br>Ralf Seepold                      | 45 |

| 5.  | Virtual Development Environment for Embedded<br>Systems Using ARMulator and SystemC Models<br>Sang-Young Cho and Jeong-Bae Lee                            | 59 |

| II. | Embedded Programming                                                                                                                                      | 73 |

| 6.  | Rule-Set-Extraction from C-Code<br>Franz Wotawa and Willibald Krenn                                                                                       | 75 |

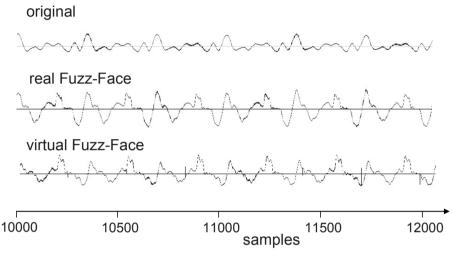

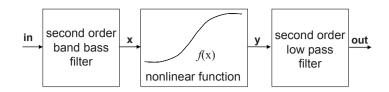

| 7.  | Real Time Implementation of Fuzz-Face Electric Guitar Effect<br>Massimo Conti, Simone Orcioni, Marco Caldari and Franco Ripa                              | 89 |

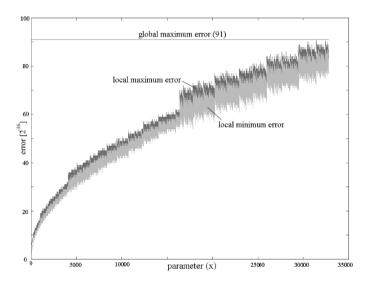

| 8.   | Providing Standardized Fixed-Point Arithmetics for<br>Embedded C Programs                                                                                                                               | 101 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | Wilfried Elmenreich, Andreas Wolf and Maximilian Rosenblattl                                                                                                                                            |     |

| III. | Middleware Platforms                                                                                                                                                                                    | 115 |

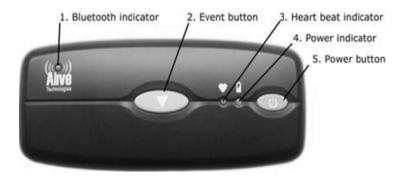

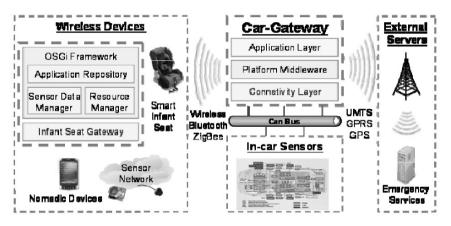

| 9.   | A Home E-Health System for Dependent People Based on<br>OSGi<br>Jaime Martín, Ralf Seepold, Natividad Martínez Madrid,<br>Juan Antonio Álvarez, Alejandro Fernández-Montes and<br>Juan Antonio Ortega   | 117 |

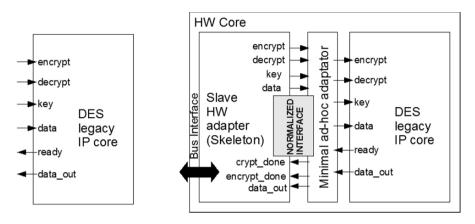

| 10.  | Transparent IP Cores Integration Based on the Distributed<br>Object Paradigm<br>Fernando Rincón, Jesús Barba, Francisco Moya,<br>Félix J. Villanueva, David Villa, Julio Dondo and<br>Juan Carlos López | 131 |

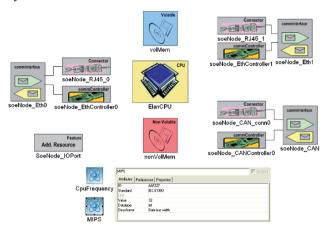

| 11.  | Platform Modeling in Safety-Critical Embedded Systems<br>Bernhard Huber and Roman Obermaisser                                                                                                           | 145 |

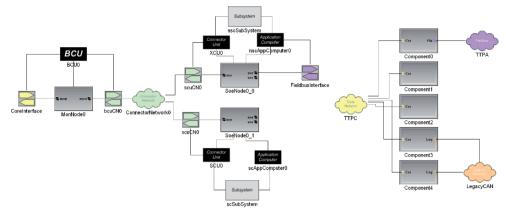

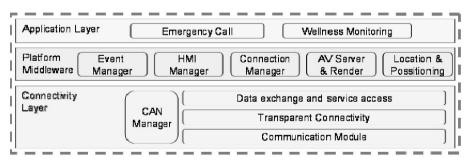

| 12.  | Service Platform for E-Safety Automotive Intelligent System<br>Jesús Sáez, Alvaro Reina, Ralf Seepold,<br>Natividad Martínez Madrid, Alberto Los Santos,<br>Pilar Sanz, Imran Sabir and Henk Aarts      | 159 |

| IV.  | Sensor Networks and Autonomous Systems                                                                                                                                                                  | 173 |

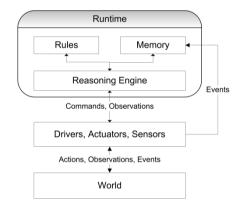

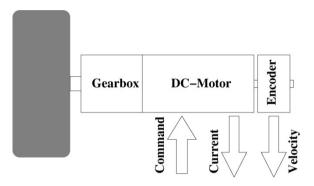

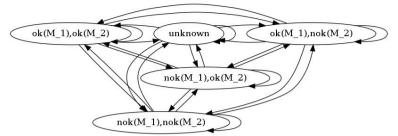

| 13.  | Intelligent, Fault Adaptive Control of Autonomous Systems<br>Willibald Krenn and Franz Wotawa                                                                                                           | 175 |

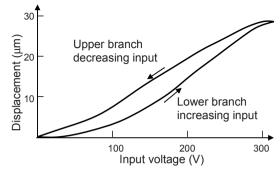

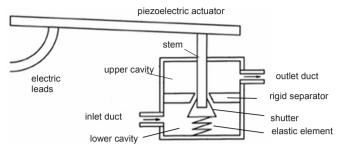

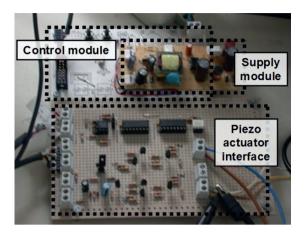

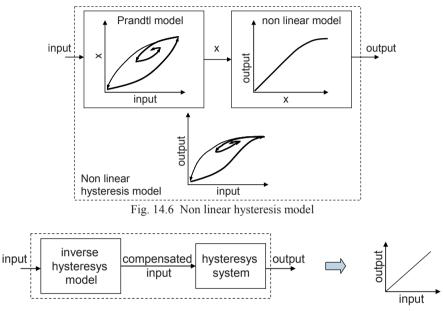

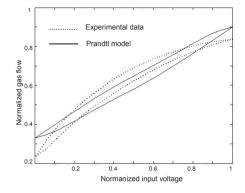

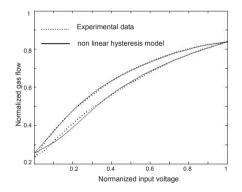

| 14.  | Digital Open-Loop Control of a Piezoelectric Valve for<br>Household Appliances<br>Daniele Petraccini, Massimo Conti, Fortunato Nocera,<br>Lorenzo Morbidelli and Fabrizio Concettoni                    | 189 |

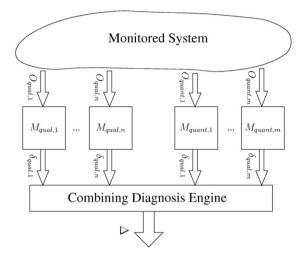

| 15.  | Coming Quantitative and Qualitative Models with Active<br>Oberservations to Improve Diagnosis of Complex Systems<br><i>Gerald Steinbauer and Franz Wotawa</i>                                           | 203 |

| Contents |                                                                                                                                                                        |     |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| v.       | Intelligent Engineering                                                                                                                                                | 217 |

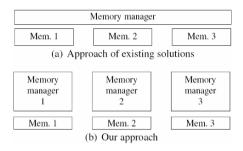

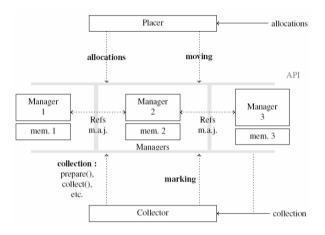

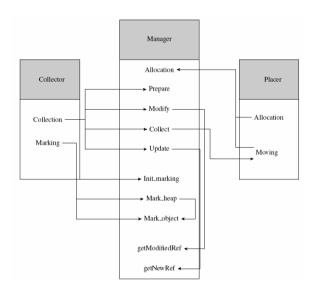

| 16.      | Object Memory Management for Constrained Devices with<br>Heterogeneous Memories<br><i>Kevin Marquet and Gilles Grimaud</i>                                             | 219 |

| 17.      | Efficient Computation of Min and Max Sensor Values<br>in Multihop Networks<br>Nuno Pereira, Björn Andersson, Eduardo Tovar and<br>Paulo Carvalho                       | 233 |

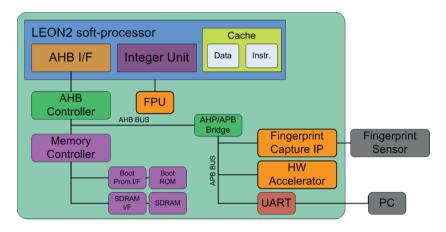

| 18.      | A Low-Cost FPGA-Based Embedded Fingerprint Verification<br>and Matching System<br><i>Maitane Barrenechea, Jon Altuna, Mikel Mendicute and</i><br><i>Javier Del Ser</i> | 247 |

| 19.      | FPGA-Rootkits<br>Markus Kucera and Michael Vetter                                                                                                                      | 261 |

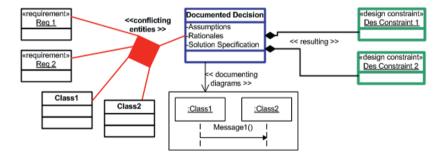

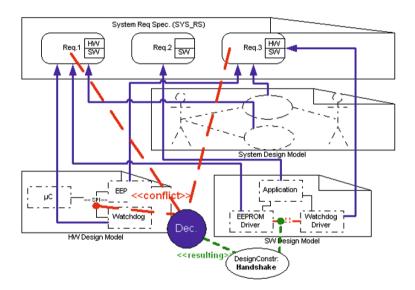

| 20.      | Bridging the Requirements to Design Traceability Gap<br>Bernhard Turban, Markus Kucera, Athanassios Tsakpinis and<br>Christian Wolff                                   | 275 |

## Contributors

Henk Aarts Jon Altuna Juan Antonio Álvarez Björn Andersson Jesús Barba Maitane Barrenechea Marco Caldari Paulo Carvalho Antón Civit Fabrizio Concettoni Massimo Conti Javier Del Ser Julio Dondo Wilfried Elmenreich Alejandro Fernández-Montes Gilles Grimaud Bernhard Huber Mario Ibáñez Willibald Krenn Markus Kucera Gabriel Jiménez Jeong-Bae Lee Alejandro Linares-Barranco Juan Carlos López Alberto Los Santos Carlos Luján-Martínez Kevin Marquet Jaime Martín Javier Martínez

Natividad Martínez Madrid Mikel Mendicute Lorenzo Morbidelli Francisco Moya Fortunato Nocera Roman Obermaisser Simone Orcioni Juan Antonio Ortega Nuno Pereira Daniele Petraccini Alvaro Reina Fernando Rincón Franco Ripa Maximilian Rosenblattl Imran Sabir Jesús Sáez Pilar Sanz Ralf Seepold Gerald Steinbauer Eduardo Tovar Athanassios Tsakpinis Bernhard Turban Michael Vetter David Villa Félix J. Villanueva Andreas Wolf Christian Wolff Franz Wotawa Sang-Young Cho

## Reviewers

Massimo Conti Università Politecnica delle Marche, Ancona, Italy

Wilfried Elmenreich University of Klagenfurt, Austria

Natividad Martínez Madrid Universidad Carlos III de Madrid, Spain

Ralf E.D. Seepold Universidad Carlos III de Madrid, Spain Part I

Multimedia Systems

## Chapter 1

## Smart Wireless Image Sensors for Video Surveillance

Massimo Conti and Simone Orcioni

DIBET, Università Politecnica delle Marche, Ancona, Italy, m.conti@univpm.it

Abstract This chapter presents an analysis of image processing performance analysis of wireless image sensors networks for video surveillance. The dependence of image quality, network throughput and channel noise sensitivity with image enhancement algorithms, image compression and wireless protocols have been investigated. The objective of the work is to give useful guidelines in the design of image wireless networks over low cost, low power, low rate Bluetooth and Zigbee wireless protocols.

Keywords Image processing, Video surveillance, Wireless network, Bluetooth, Zigbee.

## 1.1 Introduction

Nowadays image sensors based on CMOS technology are very common in portable devices. They present many useful characteristics offering low-power and low-cost features as well as high quality. The problem of improving the quality of images acquired in critical illumination conditions is interesting for consumer video, photo camera applications and for video surveillance applications. As a consequence, there is a growing interest on efficient and low complexity implementations of nonlinear algorithms for image enhancement [1].

Research on sensor networks was originally motivated by military applications; however the availability of low-cost sensors and communication networks has resulted in the development of many other potential applications, like Infrastructure Security, Environment and Habitat Monitoring, Health Monitoring, Industrial Sensing and Traffic Control [2,3].

N. Martínez Madrid, R.E.D. Seepold (eds.), Intelligent Technical Systems, Lecture Notes

in Electrical Engineering 38, DOI 978-1-4020-9823-9\_1,

<sup>©</sup> Springer Science+Business Media B.V. 2009

This contribution focuses on the analysis of image processing algorithms for wireless networks of smart low power image sensors for video surveillance.

A sensor network design is influenced by many factors, which include fault tolerance, scalability, production costs, operating environment, hardware constraints and power consumption [4–6]. These factors are important because they serve as a guideline to design the protocol, the network topology, the processing performed by each sensor, the data to be transmitted, the application layer, the hardware/software implementation of the transmitter and receiver and of the image processing.

Video surveillance recently is becoming one of the promising applications for wireless networks [7–18]. Hengstler [16] presented a tool based on Matlab for investigation and development of applications for wireless sensor networks.

In Hengstler et al. [17], a smart camera architecture is presented for local processing, with the aim of facilitating distributed intelligent surveillance. The paper focuses mainly on the efficient data link layer utilizing IEEE 802.15.4 MAC for enabling data exchange between smart cameras.

The IBM smart surveillance system [18] is able to monitor, manage surveillance data, detect, track and classify objects, with the possibility to manage in real time the surveillance system on the Web. But the aspect of low power for implementation on battery supplied wireless cameras is not addressed in the system.

The wireless sensor node can usually be equipped with a limited power source. Sensor node lifetime, therefore, shows a strong dependence on battery lifetime. The switching off of few nodes in a sensor network can cause significant topological changes and might require a re-organization of the network. Hence, power management requires additional importance. For these reasons researchers are currently focusing on the design of poweraware protocols and algorithms for sensor networks.

The main task of a sensor node in a sensor field is to detect events, perform quick local data processing, and then transmit the data. Power consumption can hence be divided into three domains: sensing, communication, and data processing.

Sensing power varies with the nature of applications. Sporadic sensing might consume less power than constant event monitoring. The complexity of event detection also plays a crucial role in determining energy dissipation.

The main specifications to be considered in the design of image sensor wireless networks are the quality of the image to be transmitted, the number of images per second that can be transmitted, the power dissipated for image processing and transmission and the insensitivity with noise in the channel. Image processing algorithms, image compression algorithms, sensor node architecture, wireless protocol from application layer to physical layer, network topology must be analyzed and all parameters should be tuned in a system level simulation of the complete sensor network in order to optimize the performances of the complete system.

Image compression in the sensor reduces data to be transmitted, but this causes a reduction in image quality and a greater sensitivity to noise. Conversely, image processing can be performed to improve quality before compression in the sensor, but the processing will increase the power dissipated by the sensor itself and the compression ratio will be reduced with a consequent increment in the transmission power and sensitivity to noise. Image processing on the receiver side, after applying compression, does not allow the same quality, but it reduces power dissipation on the sensor node.

This work presents an analysis of the dependence of image quality, network throughput, and channel noise sensitivity with image enhancement algorithms, JPEG image compression parameters and wireless protocols. In particular ZigBee and Bluetooth wireless standard will be considered.

In Section 1.2 the architecture of the smart wireless sensor node is presented, and some results obtained with Matlab simulations are shown. Section 1.3 briefly presents the ZigBee and Bluetooth wireless standards and shows an analysis of the performance of a wireless sensor network obtained with Matlab and SystemC.

#### **1.2 Smart Wireless Image Sensor**

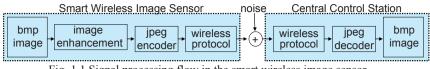

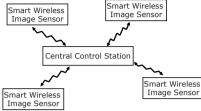

The processing flow of a Smart Wireless Image Sensor is reported in Fig. 1.1. Before JPEG compression, the image is processed by an image enhancement algorithm, then the data are coded following the wireless protocol, and noise in the channel can be added. Image enhancement is applied to improve the quality of the image for successive image recognition on the central control station.

In video surveillance a key aspect is the improvement in image quality in bad illumination conditions. For example, it is extremely important to identify details in a not illuminated part of the image, when another part of the image is extremely illuminated. A lot of work is devoted to this kind of problem which takes inspiration from the retinex algorithm of Land [19]. Following the retinex approach the image I(x,y) is considered as the product of two terms: the illumination L(x, y) and the reflectance R(x, y). The retinex algorithm requires the calculus of very complex functions, such as logarithm, exponential function and division, functions that are very expensive in terms of power dissipation and hardware complexity.

Fig. 1.1 Signal processing flow in the smart wireless image sensor

Recently a simplified version of the retinex algorithm has been developed [20] with a strong reduction in the complexity, but acceptable quality in image processing. The low complexity and low power dissipation of this simplified algorithm, that we will call "nonlinear stretching" in the rest of the paper, allow the implementation of image processing in the sensor.

The quality of the image can be improved with nonlinear stretching algorithm, even in case of image compression, if image processing is performed before compression.

Widely used image compression algorithms are JPEG and JPEG2000. The effect on the image quality with JPEG and JPEG2000 compression over a ZigBee network has been investigated [21], with the conclusion that JPEG2000 reaches better quality, but with the cost of much higher complexity. JPEG should be preferred, if the key aspects are the low cost and low power of the sensor node, as it is in our goal.

In this work we will compare retinex [19] and nonlinear stretching [20] image enhancement algorithms for different values of quality JPEG compression in presence of errors in the data stream due to noise in the channel. The measure used for the quality of image processing is the PSNR:

$$PSNR = 10\log_{10}\left[\frac{2^{2k}}{MSE}\right]$$

(1.1)

where k is the number of bits representing each pixel, and MSE is the mean square error defined as

$$MSE = \frac{1}{n \cdot m} \sum_{i=1}^{n} \sum_{j=1}^{m} \left( I_1(i,j) - I_2(i,j) \right)^2$$

(1.2)

where n and m are the dimensions of the images and I1 and I2 are the images to be compared. Many black and white images have been used to verify the quality of the algorithm. The simulations have been performed in MATLAB.

Figure 1.2a reports an original black and white image in windows bitmap (bmp) format (320×240, black and white, 8 bit resolution, 76.800 bytes), that can be a good test for critical illumination conditions in video surveillance. Figure 1.2b reports the original image after a JPEG compression with 20% quality. Figure 1.2c reports the image after a jpeg compression with 20% quality, successive to the nonlinear stretching. Figure 1.2d reports the image

after a jpeg compression with 20% quality successive to a retinex processing, the improvement in the quality of the dark areas is evident and the contrast is higher if compared to the nonlinear stretching algorithm. In all the cases the effect of the strong JPEG compression (Q20) after image enhancement does not reduce; the quality of the image in an evident way.

(e) nonlinear stretching after JPEG Q20 (f) retinex after JPEG Q20. Fig. 1.2 Image after different processing and compression tasks Image enhancement (low complexity nonlinear stretching or retinex) must be performed to recognize the details of the image, indispensable for video surveillance. To verify the possibility to implement the image enhancement not in the sensor but in the receiver that has no energy limitations, we implemented the enhancement after JPEG compression, indispensable for reducing data rate and transmission power.

Figure 1.2e reports effects of nonlinear stretching applied to the image after a JPEG compression with 20% quality; and in Figure 1.2f retinex is applied to the image after a JPEG compression with 20% quality. The details of the image are no more visible. This means that the image enhancement must be performed in the image sensor before JPEG compression.

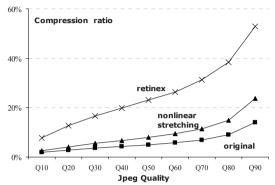

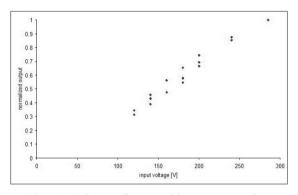

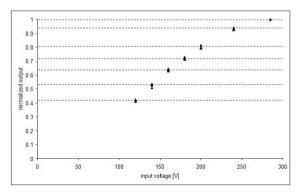

Figure 1.3 reports the compression ratio achieved applying JPEG to the original bmp image and after nonlinear stretching or retinex algorithms are applied, for different values of JPEG compression. The image enhancement, increasing the details, reduces the JPEG compression, as expected. But in the nonlinear stretching case, the compression is still very high.

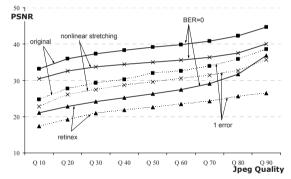

Figure 1.4 reports the PSNR in dB for different values of the quality of JPEG compression and for the original, after nonlinear stretching or after retinex algorithms are applied. As an example the difference between the original (Figure 1.2a) and compressed image (Figure 1.2b) expressed in PSNR is 36 dB, while the PSNR between the retinex transformed image and compressed of retinex transformed image (Figure 1.2d) is 23 dB. This means that the image enhancement algorithm makes the JPEG compression critical.

Statistical simulation has been performed inserting in a random position errors in the images and the PSNR has been calculated. Figure 1.4 reports the average values over 1000 simulations of the PSNR when an error of only 1 bit is inserted in each image, for different values of the quality of JPEG compression.

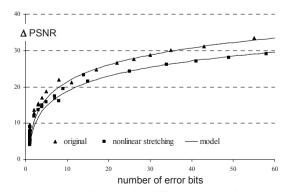

Figure 1.5 reports the decrement in the PSNR ( $\Delta$ PSNR) as a function of the number of bits of error inserted in each image. The dots represent the numerical simulations with different values of JPEG compressions. The dependence of  $\Delta$ PSNR with JPEG quality is not relevant, as can be seen from Figs. 1.4 and 1.5. The statistical simulation shows that the degradation of the quality of the image does not strongly depend on the JPEG compression quality or on the size of the image but on the number of bits of error inserted. The image quality is still acceptable for video surveillance applications for a PSNR higher than 20dB corresponding to about 5 bits of error inserted in the image. From the simulations the following model of  $\Delta$ PSN has been derived as a function of the *n<sub>e</sub>* number of bits of error inserted in the image

$$\Delta PSNR = a + b \ln(n_{a}) \tag{1.3}$$

The model is shown in Fig. 1.5, the parameters a and b are obtained fitting the experimental data.

Fig. 1.3 Compression ratio with respect to the original bmp image

Fig. 1.4 PSNR in dB for different values of the JPEG quality, for the original, after nonlinear stretching or after retinex are applied, with an error of 1 bit and without errors

Fig. 1.5 Decrement in PSNR in dB for different values of errors in the image

#### 1.3 Wireless Image Sensor Network Performance Analysis

A great number of standards have been defined for wireless communications, each one for different applications and with different characteristics.

Between them, widely used are the WiFi, Bluetooth, Home-RF, ZigBee, Wireless USB and Certified Wireless USB. In this work we will study the performance of Bluetooth [22] and ZigBee [23–25] for video surveillance applications, the topology considered is a star connection, as shown in Fig. 1.6 with images transmitted from the sensors to the central control station.

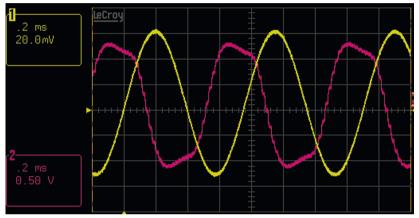

Bluetooth (IEEE 802.15.1) is mainly used for devices that have regular charge (e.g. mobile phones) and in applications like: hands-free audio, file transfer. The data rate is 1 Mb/s using a 1-MHz channel with an effective maximum bandwidth of 721kb/s. Bluetooth operates under a Time Division Duplex (TDD) polling scheme with a Frequency Hopping Spread Spectrum (FHSS) technique, with Gaussian Frequency Shift Keying (GFSK) modulation. Bluetooth allows many degrees of freedom to the designer, such as the choice of the different type of packets (DH1, DH3, DH5, DM1, DM3, DM5).

The ZigBee (IEEE 802.15.4) standard has been developed specifically for remote monitoring and control. ZigBee networks are designed to save the power of the slave nodes. For most of the time, a slave device is in deepsleep mode and wakes up only for a fraction of time to confirm its presence in the network. The targets of ZigBee are low cost applications where the battery cannot be changed (battery life time of 1-2 years) with limited requirements of bandwidth. The maximum packet size is 133 bytes, but only 102 bytes can be used for data transmission. The supported nominal data rates are 250 kb/s, and the effective maximum date rate is about 190 kb/s. The ZigBee MAC layer uses the CSMA-CA algorithm to access the channel: each device tries to use the channel after a random delay. This algorithm yields high throughput and low latency for low duty cycle devices, like sensors and controls. Unfortunately the CSMA-CA algorithm reduces the effective maximum information rate to about 125 kbps in case of a single node that uses the channel. ZigBee is preferable for a network infrequently used and passing small data packets.

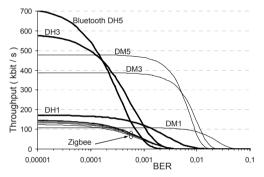

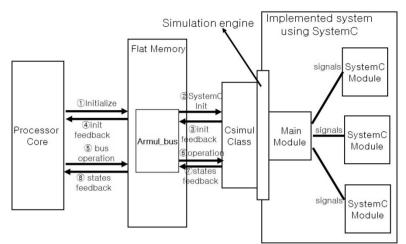

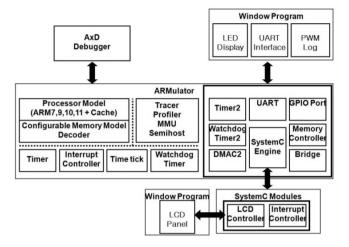

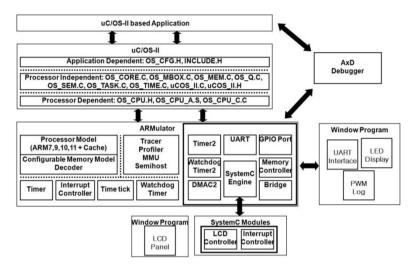

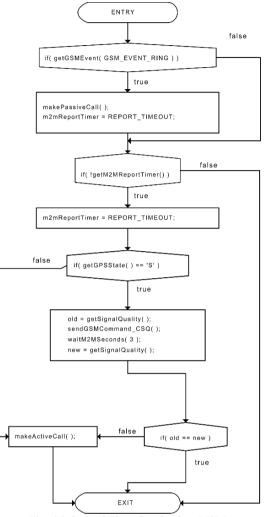

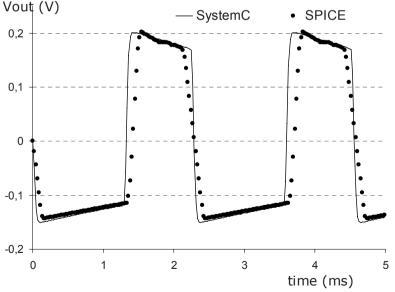

The Lower layers of Bluetooth and ZigBee have been implemented in SystemC [26–28]. Figure 1.7 shows the maximum network throughput as a function of the BER for Zigbee and Bluetooth, for different number of sensors (from 1 to 6) and for different types of Bluetooth packets. The data have been obtained with SystemC simulations [26, 27] and similar data are reported for the Bluetooth standard [29]. We considered a star topology with

1 master and n slaves, continuously transmitting images to the master. In a Bluetooth network the maximum throughput is independent of the number of slaves, therefore in Fig. 1.7 only one line can be seen for each type of Bluetooth packet.

Fig. 1.6 Smart wireless sensor network topology

Fig. 1.7 Effective network throughput of Bluetooth and Zigbee as a function of the BER

Fig. 1.8 BER as a function of signal to noise ratio for Bluetooth and Zigbee

In a Zigbee network the maximum throughput increases lightly with the number of sensors due to the CSMA-CA algorithm, therefore 6 curves are visible in Fig. 1.7 for the Zigbee network: the lower one corresponds to the network with 1 coordinator and 1 sensor, the upper one corresponds to the network with 1 coordinator and 6 sensors. The throughput of the Zigbee

network is, in general, lower than Bluetooth throughput: the best type of Bluetooth packet depends on the BER.

The DM packets use 10/15 FEC with CRC allowing a correction of one bit of error for each 10 bit of data with the cost of reduction of throughput without errors; conversely the effective throughput is higher for DM packets with respect to DH packets for high values of BER. Bluetooth gives higher bandwidth, but the cost and the power dissipation for transmission and for the protocol processing is higher with respect to Zigbee.

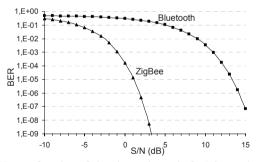

Figure 1.8 shows the BER as a function of the signal to noise ratio for Bluetooth and Zigbee obtained from the 802.15.4 specifications [24,25], and it shows that Zigbee coding is more robust in presence of noise with respect to Bluetooth.

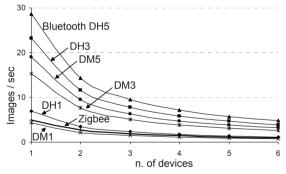

The number of images per second that can be transmitted by each sensor in the network depends on the size of the image, on the protocol, on the noise and on the number of devices in the network. As an example we consider the transmission of the image shown in Fig. 1.2c, that is the after nonlinear stretching and JPEG Q20 compression with a size of 25216 bits. In previous section, in particular in Figs. 1.3 and 1.4, it has been evidenced that nonlinear stretching with JPEG Q20 is a good compromise allowing good quality of image for video surveillance purposes, strong size reduction with respect to the 614400 bits of the original bmp image, and reduced decrement of PSNR in presence of noise.

Fig. 1.9 Number of images per second that can be transmitted by each sensor as a function of the number of sensors in the network, for a Zigbee network and a Bluetooth network with different type of packets

Figure 1.9 shows the number of images (25216 bit size) per second that can be transmitted in absence of noise in the channel by each sensor as a function of the number of sensors in the network, for a Zigbee network and a Bluetooth network with different types of packets. In a Bluetooth network the throughput from each sensor to the master is simply the throughput achievable in the case of a network with only one sensor divided by the number of sensors. In a Zigbee network, due to the randomness of the CSMA-CA channel access algorithm, the throughput from each sensor is higher than the throughput achievable in the case of a network with only one sensor divided by the number of sensors.

An analysis of the images sent in the networks in presence of noise can be obtained combining the analysis shown in Figs. 1.3 and 1.4 that considers the image enhancement algorithms and JPEG compression factor, with the analysis shown in Figs. 1.7 and 1.8, that considers the network throughput in presence of noise.

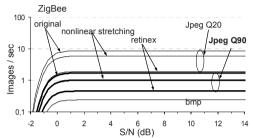

The BER in the transmission of a JPEG image degrades the quality of the image. In many cases the image cannot be recovered. This means that the image should be retransmitted. Figure 1.10 shows the number of images per second that can be send to the coordinator of a Zigbee network with 6 sensors as a function of the signal to noise ratio for the original bmp image not compressed, for the original image with JPEG Q20 and Q90 compression, for the image processed by retinex and successively compressed with JPEG Q20 and Q90, and finally for the image processed by nonlinear stretching and successively compressed with JPEG Q20 and Q90.

The number of images not compressed with JPEG (bmp in Fig. 1.10) per second is extremely low. The choice of a suitable image enhancement algorithm and the JPEG compression factor is important not only for the image quality but also for the image rate, and consequently for the power dissipation. The image rate can be improved 70 times with respect to bmp image, allowing the use of Zigbee for video surveillance applications. The Zigbee coding is efficient even in presence of noise, as shown in Fig. 1.8, therefore the image rate is degraded only with high values of noise.

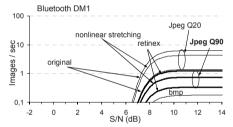

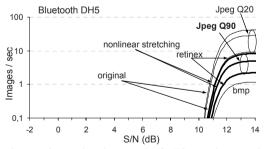

Figures 1.11 and 1.12 show the same results of Fig. 1.10 but for a Bluetooth Network using DM1 and DH5 packets, respectively. The DM1 packets give the lower data rate with respect to the other Bluetooth packets; therefore the performances are worse than Zigbee even with low values of noise. Conversely the data rate of DH5 packets is strongly dependent on noise. Good results are evidenced using DH5 packets with low values of noise but the Zigbee performances are much more insensitive to noise.

#### 1.4 Conclusions

Many simulations have been performed to investigate the effect on PSNR and on ZigBee and Bluetooth data rate of the parameters of JPEG compression for different image enhancement algorithms and in presence of noise in the channel. In conclusion the retinex algorithm is more sensitive to the noise with respect to the nonlinear stretching that gives good image enhancement even with JPEG compression and in presence of noise.

Both ZigBee and Bluetooth protocols are suitable for video surveillance applications; Zigbee seems to be more robust to noise with respect to Bluetooth. Conversely the frequency hopping technique used by Bluetooth makes the network more insensitive to the interference with other 2.4GHz networks.

Fig. 1.10 Images / s that can be send to the coordinator of a Zigbee network with 6 sensors as a function of S/N for different image processing in the sensor

Fig. 1.11 Images / s that can be send to the master of a Bluetooth network using DM1 packets as a function of S/N for different image processing in the sensor

Fig. 1.12 Images / s that can be send to the master of a Bluetooth network using DH5 packets as a function of S/N for different image processing in the sensor

#### References

- L.-W. Lai, C.-H. Lai, Y.-C. King, "A Novel Logarithmic Response CMOS Image Sensor with High Output Voltage Swing and In-Pixel Fixed-Pattern Noise Reduction", IEEE Sensors Journal, 4(1), 122–126, Feb. 2004.

- 2. I.F. Akyildiz, W. Su, Y. Sankarasubramaniam, E. Capirci, "Wireless Sensor Networks: A Survey", Computer Networks 38, 393–422, 2002.

- C.-Y. Chong; S.P. Kumar, "Sensor networks: evolution, opportunities, and challenges", Proceedings of the IEEE, 91(8), Aug. 2003.

- 4. A.P. Chandrakasan, R. Min, M. Bhardwaj, S.H. Cho, A. Wang, Power Aware Wireless Microsensor Systems, keynote Paper ESSCIRC, Florence, Italy, September 2002.

- K. Sohrabi, J. Gao, V. Ailawadhi, G.J. Pottie, Protocols for Self-Organization of a Wireless Sensor Network, IEEE Personal Communications, Vol. 7, No. 5, Oct. 2000.

- W. Ye, J. Heidemann, D. Estrin, An Energy-Efficient MAC Protocol for Wireless Sensor Networks, In Proceedings of the 21st International Annual Joint Conference of the IEEE Computer and Communications Societies (INFOCOM 2002), New York, NY, USA, June, 2002.

- L. Hampapur, J. Brown, A. Connell, N. Ekin, M. Haas, H. Lu, S. Merkl, S. Pankanti, "Smart Video Surveillance: Exploring the Concept of Multiscale Spatiotemporal Tracking," IEEE Signal Processing Mag., 22(2), 38–51, Mar. 2005.

- G.L. Foresti, C. Micheloni, L. Snidaro, P. Remagnino, T. Ellis, "Active Video-Based Surveillance System: The Low-Level Image and Video Processing Techniques Needed for Implementation," IEEE Signal Processing Mag., vol. 22, no. 2, pp. 25–37, Mar. 2005.

- R. Kleihorst, A. Abbo, V. Choudhary, B. Schueler, "Design Challenges for Power Consumption in Mobile Smart Cameras," in Proc. COGnitive Systems with Interactive Sensors (COGIS 2006), Mar. 2006.

- M. Rahimi, R. Baer, O.I. Iroezi, J.C. Garcia, J. Warrior, D. Estrin, M. Srivastava, "Cyclops: In Situ Image Sensing and Interpretation in Wireless Sensor Networks," in Proc. 3rd International Conference on Embedded Networked Sensor Systems (SenSys 2005), Nov. 2005, pp. 192–204.

- F. Dias Real de Oliveira, P. Chalimbaud, F. Berry, J. Serot, F. Marmoiton, "Embedded Early Vision Systems: Implementation Proposal and Hardware Architecture," in Proc. COGnitive systems with Interactive Sensors (COGIS 2006), Mar. 2006.

- I. Downes, L. Baghaei Rad, H. Aghajan, "Development of a Mote for Wireless Image Sensor Networks," in Proc. COGnitive Systems with Interactive Sensors (COGIS 2006), Mar. 2006.

- Z.-Y. Cao, Z.-Z. Ji, M.-Z. Hu, "An Image Sensor Node for Wireless Sensor Networks," in Proc. International Conference on Information Technology: Coding and Computing (ITCC 2005), 2, 740–745, Apr. 2005.

- R. Kleihorst, B. Schueler, A. Danilin, M. Heijligers, "Smart Camera Mote with High Performance Vision System," ACM SenSys 2006 Workshop on Distributed Smart Cameras (DSC 2006), Oct. 2006.

- M. Bramberger, A. Doblander, A. Maier, B. Rinner, H. Schwabach, "Distributed Embedded Smart Cameras for Surveillance Applications," in IEEE Computer Mag., 39(2), 68–75, Feb. 2006.

- S. Hengstler and H. Aghajan, "WiSNAP: A Wireless Image Sensor Network Application Platform", 2nd Int. Conf. on Testbeds and Research Infrastructures for the Development of Networks and Communities (TridentCom), March 2006.

- 17. S. Hengstler, D. Prashanth, S. Fong, H. Aghajan, "MeshEye: A Hybrid-Resolution Smart Camera Mote for Applications in Distributed Intelligent Surveillance", Information Processing in Sensor Networks (IPSN-SPOTS), April 2007.

- L. Brown, J. Connell, A. Hampapur, M. Lu, A. Senior, C.-F. Shu, Y. Tian, "IBM Smart Surveillance System (S3): A Open And Extensible Framework For Event BasedSurveillance", Proc. of the Int. Conf. on Advanced Video- and Signal-based Surveillance September 2005.

- 19. E.H. Land, "Recent Advances in Retinex Theory", Vision Research, 26(1), 7–21, 1986.

- T. Balercia, A. Zitti, H. Francesconi, S. Orcioni, M. Conti, "FPGA implementations of a simplified Retinex image processing algorithm", Proc. of IEEE ICECS '06 Int. Conf. on Electronics, Circuits and Systems, Nice, France, pp.176–9, December 10–13 2006.

- G. Pekhteryev, Z. Sahinoglu, P. Orlik, G. Bhatti, "Image transmission over IEEE 802.15.4 and ZigBee Networks", Proc. of IEEE ISCAS 2005, Kobe, Japan. pp.3539– 3542.

- 22. Bluetooth SIG, "Specification of the Bluetooth system version 1.1," Feb 2001.

- 23. "ZigBee White Paper" and "ZigBee Specifications" in www.zigbee.org

- 24. IEEE 802.15.4TMStd.- 2003 Wireless Medium Access Control and Physical Layer Specifications for Low-Rate Personal Area Networks (WPANs).

- 25. IEEE 802.15.4TM Std.-2006- Revision of IEEE 802.15.4TM Std. 2003.

- M. Caldari, M. Conti, P. Crippa, G. Marozzi, F. Di Gennaro, S. Orcioni, C. Turchetti, "SystemC Modeling of a Bluetooth Transceiver: Dynamic Management of Packet Type in a Noisy Channel" Proc of DATE 2003, Munchen, pp.214–219.

- M. Conti, D. Moretti, "System Level Analysis of the Bluetooth Standard", Proc of DATE 2005, München, 3, 118–123.

- A. Mignogna, M. Conti, M. D'Angelo, M. Baleani, A. Ferrari, "Transaction Level Modeling and Performance Analysis in SystemC of IEEE 802.15.4 Wireless Standard" DSD'2008, Proc. of Euromicro Conf. on Digital System Design, 3–5 September, 2008, Parma, Italy.

- T.Y. Chui, F. Thaler, W.G. Scanlon, "A Novel Channel Modeling Technique for Performance Analysis of Bluetooth Baseband Packets", ICC 2002. IEEE International Conf. on Communications 2002, 1, 308–312, 28 April-2 May 2002.

## Chapter 2

## Policy Management Architecture for Multimedia Services in a Multi-Provider Scenario

Mario Ibáñez, Natividad Martínez Madrid and Ralf Seepold

Universidad Carlos III de Madrid, 28911 Leganés (Madrid), Spain, mario.ibanez@uc3m.es, natividad.martínez@uc3m.es, ralf.seepold@uc3m.es

Abstract The management of multimedia services integrated into a service platform has been taken as a starting point for the development of a new model that supports virtualization of the platform concept. The virtualization of provider dependent configuration frameworks is introduced to isolate different service providers during the installation and maintenance of new services contracted by the end user. In addition, the virtualization has to be enhanced with a system that provides a management of common resources and the way of accessing to them. That is made with a set of policy management rules and procedures that are described in this paper. The model has been evaluated in a multi-provider case study with focus on multimedia data management.

Keywords Service platforms, Residential gateways, Policy management.

## 2.1 Introduction

Multimedia services are arriving to our homes. Each month, new offers of Video on Demand, TV over IP, etc. are being including in the service catalogue of the telecom operators. It is important to enable a proper infrastructure to the deployment of these services in the home. Therefore, this infrastructure needs also to take into account that multiple multimedia services arrive concurrently to the home network and it is needed to maintain a certain *Quality of Service* (QoS).

The coexistence of multiple services demands a platform that is dynamically managing the life cycle of all services. The OSGi platform

in Electrical Engineering 38, DOI 978-1-4020-9823-9 2,

© Springer Science+Business Media B.V. 2009

provides a framework for the execution and management of services.<sup>a</sup> This service platform allows installing and uninstalling different services in the same device, the Residential Gateway (RGW). The RGW is placed at the border of the home network and manages data flows that enter or leave the home environment. Those flows correspond among others to multimedia services that are managed by the applications installed in the OSGi platform.

In an open market, all services that the user has contracted can be served by more than one service provider. This fact draws a different scenario in which different administrators have to manage the RGW. Shared management of a system is a complex task, with several consequences for security. Different solutions decide to avoid or prohibit by definition more than one user management of the RGW, limiting in this way the business models and functionality. On the contrary, this chapter presents a solution that allows to provide this kind of behavior. The solution consists in the creation of new virtual platforms placed over the service platform to provide isolation to the management of each administrator. That means that every administrator of the service platform can modify its applications in the RGW without the intervention of any other administrator.

In Section 2.2, the state of the art is presented and the OSGi technology is introduced. In Section 2.3, the working scenario is presented and roles are described in detail. Section 2.4 presents the software architecture of the solution and Section 2.5 summarizes the results obtained. Finally, Sections 2.6 and 2.7 summarize the chapter and future work is presented.

## 2.2 State of the Art

The proposed management architecture is based on the OSGi service platform which is used to manage services and hosts the management and the virtualization systems of the platform. The next sections present an analysis of related research work and a summary the relevant characteristics of OSGi.

## 2.2.1 Related Work

The work presented in this paper concentrates on the development of a service platform for a RGW oriented to multimedia services. A basic model of a service platform has been presented by Hofrichter [1] and Waring [2]; a

a http://www.osgi.org

more complete and also updated definition is given by the Home Gateway Initiative (HGI) [3]. Since service provisioning is relevant also for a multiprovider scenario, a simple scenario based on OSGi is presented by Dueñas [4]. It describes a scenario with different users involved in the management and deployment of services in the RGW. Furthermore, two main users are defined; the operator and the service provider. The operator is in charge of managing the RGW and the service provider is in charge of providing services. However, the service provider cannot manage services in the RGW. This approach lacks support for multiple users managing the platform at the same time but it presents a first approach to the management of RGW.

A different management approach is presented by Cho [5]. In this model, the management of services is tackled as a policy access problem and it is solved using the Role-Based Access Control (RBAC) model. This model defines users, sessions, roles, permission and the associations between those entities. Surrounding this model, an infrastructure and a protocol is created to provide permission to service providers for managing services in the RGW. The model includes an access provider who defines access rights for the different service providers. The end users contract services, the model notifies changes and enables the required permissions. This model is also based on the assumption that only one of the different types of users has the full control and thus takes the final decisions about the RGW configuration. Again, this is not a multi-manager approach.

Finally, there is another relevant approach [6] that proposes different users being members of the RGW management at the same time. In addition, this paper proposes a concept of virtual platforms. Isolation is the basic mechanism to separate different users and thus to avoid interaction. There are only two different managers of the RGW, the operator controlling the service platform and authorizes the service providers, while the service providers actuate as users that can manage the virtual platforms. This approach does not support an end user managing own bundles.

The solution shown in this chapter is based on the concept of virtualization as the way of isolating different managers (access providers, service providers, end users and system vendors). These managers can simultaneously access to the RGW and configure its behavior modifying the basic parameters of the router or installing new services. This is possible due to the design of a new virtualization bundle installed in the OSGi platform. This bundle provides the needed abstraction over the router and OSGi platforms while providing isolation to the different virtual platforms. This model is based on classical virtualization techniques.

### 2.2.2 The Open Service Gateway Initiative

OSGi [7] has been selected as the platform for the services in the RGW. The OSGi specifications define a standardized, component oriented, computing environment for networked services. Adding an OSGi Service Platform to a networked device (embedded as well as servers) enables the capability to manage the life cycle of the software components in the device from anywhere in the network.

Software components can be installed, updated, or removed on the fly without having to disrupt the operation of the device. The software components or applications are called bundles. When activated, bundles may register services to provide services to other bundles in the framework

OSGi specifications also define a way for the remote management of the platform based on two components: the Remote Manager (in the mangers side) and the Management Agent (in the RGW). There is no communication protocol predefined.

The Remote Manager is a tool provided for the operator to control the service platform. By using it, the operator can access all the functions determined in the remote management interface. However, this manager is not clearly defined in the standard, leaving a concrete implementations open, i.e. to adapt to the specific properties of the management protocols used.

The Management Agent is the system's entry point for the Remote Manager. The Management Agent is a bundle that is called a Management Bundle. It owns permission for the administration of the platform, so it can manage the life cycle of the bundles in the RGW. The platform can have more than one Management Agent, each one communicating with a different remote manager and using different management protocols.

#### 2.2.3 Virtualization

A solution based on virtualization has been developed to isolate the different management agents of each service provider. As a result, each virtual platform is managed by only one service provider. As the RGW can host several virtual platforms, it will have several service providers. In the following, the basics of virtualization are commented by Smith [8].

In general, virtualization is based in the concept of a machine being constructed over different abstractions and interfaces. An abstraction is used to ignore or simplify the lower level using a well defined interface. Virtualization is a way of relaxing the constraints and increasing the flexibility. It also constructs and isomorphism that maps a virtual system on an underlying system and differs from an abstraction because the virtualization does not necessarily hide details.

The products of the virtualization are the Virtual Machines (VM) that are layers of software on top of the real machine to support the desired virtual machine's architecture. The VM can be used to replicate systems, providing independency and isolation between each replication, or to emulate the support of cross platform software, as well as to describe architectures that do not correspond to a real machine.

A first action to be done in the design of the virtualization system is to identify the interface for the virtual machine. Once the interface has been indentified, two steps have to be taken to construct a virtual machine: Firstly, a research about how to map resources of the underlying machine, and secondly, the development of the actions which allow the communication between the real machine and the virtual machine.

## 2.3 Working Environment

To understand the work presented, it is necessary to know the environment in which this work has been carried out. Then, the device and networks involved will be defined. After that, the different roles that the user of the RGW can take will be presented, and finally, a business model is sketched out.

#### 2.3.1 Scenario Description

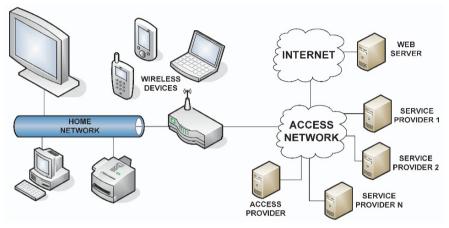

Figure 2.1 shows the key role of the RGW because it is located between the Home Network and the Access Network. Therefore, it is an ideal place to install a service platform that manages home services like for example multimedia services. Moreover, the RGW provides router functionality that connects to different networks.

As mentioned before, the OSGi framework, provides and execution environment to host application services. Due to the different services and data flows that the RGW must handle, it is necessary to install a management service allowing an easy access to the configuration data of the device. The management service provides access to the RGW configuration, like for example the data flow definition in the router or the access to the life cycle of services using OSGi.

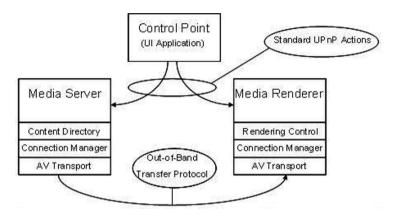

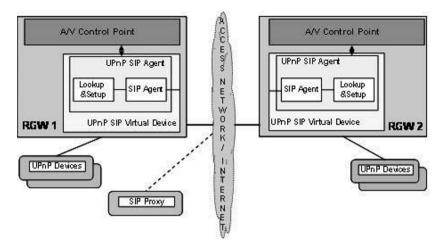

The Home Network is full of different equipment for different issues some of them are related to multimedia like TVs. These devices capable of playing or serving multimedia content require an infrastructure to share multimedia content which sometimes will arrive from outside home. The management of those multimedia flows can be implemented with different protocols, for example with UPnP installed as a service in the RGW.

The access network is managed by the access provider. This network is in charge of providing multimedia content with QoS, like it is provided by the service providers. The access network is also the entrance point for flows from Internet.

Fig. 2.1 RGW environment

In a basic scenario, the management of the access networks as well as the management of the RGWs of the end users is done by the access provider. But in a more complex scenario the service providers can manage directly the RGWs according to the services offered, while the access provider only manage the traffic in the network to maintain the QoS.

#### 2.3.2 Manager Roles

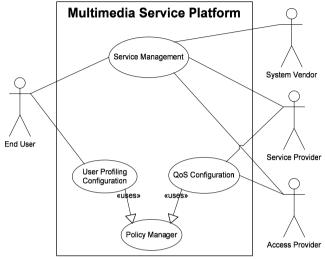

Four different managers, required for the setup of the scenario, are presented in Fig. 2.2. The access provider is in charge of ensuring the QoS in the access network. It also provides a way of connecting an end user to a service provider. So, in relation with the RGW, it can adapt the configuration of the QoS in the RGW to the needs in the network, and thus manage their applications in the platform. Basically, this application will be the one in charge of the management of the QoS.

The service provider will provide services to the end users. That means that it will be necessary to modify the QoS parameters for its own services and of course to manage its own services installed in the RGW. The service provider is not present in the initial configuration of the RGW but this role is added in the moment when a service is enabled in the RGW.

Fig. 2.2 Roles in the RGW

The system vendor is in charge of providing a service for updating the firmware of the machine. Also this role needs to access to the management of that service.

Finally, there is the end user. This role is mainly in charge of contracting new services which are later installed by the services provider in the RGW. Therefore, it needs to access to, at least, a basic configuration of its applications. In a more broad sense, it is possible to find different end users with different objectives and applications that can be managed independently. For example a leisure user that hires video on demand services and a professional user that hires bandwidth to make videoconferences with a certain QoS. This differentiation of roles forces an establishing of a user profiling configuration to define how the RGW will behave.

All data related to the configuration of QoS or profiles will be managed by a service which determines the policy to be followed by the RGW.

#### 2.3.3 Business Model

Once the scenario has been setup and the different users have been presented, a model is required that defines how relationships between them are established. We assume that the end user buys a RGW from a manufacturer or from an access provider. In case the RGW has been bought from a manufacturer it may cover a maintenance contract. The manufacturer needs to have a bundle to update the basic installation of the device. In the second case, the maintenance of the firmware can be done by the provider. In both cases, the access provider needs permission to manage the RGW.

In case other relationships are created between the end user and the access provider, the access provider has to install a bundle in the service platform to manage the QoS parameters.

A third relationship is established between service and access providers: Both agree that the service provider can use the access network to deliver services. This relation includes an agreement to maintain the QoS in the network.

The last relation is established between the end user and the service provider in order to have a service in the home. This relation also implies the installation of services in the RGW and the management of them by service providers.

## 2.4 Policy Management Architecture

The management has evolved from the management of one operator to multiple managers. Next two sections present the evolution from the monoprovider management to the multi-provider management with virtualization. Finally, details for this specific policy management are presented

#### 2.4.1 Mono-Provider Management

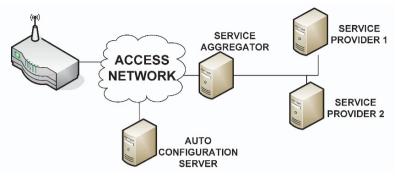

The mono-provider management scenario (cf. Fig. 2.3) presents three main devices in the access network; the RGW, the Auto-Configuration Server (ACS) and the Service Aggregator. The ACS stores the data for configuring the different services and installs them in the RGW as they are needed. The service aggregator provides a unique place from where it is possible to deploy services, although, they are owned by different service providers.

The solution implemented for the remote and automatic configuration of the RGW is based on TR-069 protocol [9] from DSL. This protocol defines a set of parameters to be exchanged between an (ACS) and the RGW to provide the configuration. Moreover, the solution is modular and compound of three bundles that provide the configuration which are briefly described in Ibáñez [10].

Fig. 2.3 Access Network in a mono-provider scenario

## 2.4.2 Multi-Provider Management

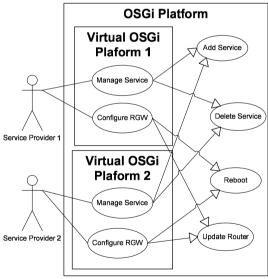

The objective of virtualization is to add mechanisms to the OSGi platform that allow having different instances of the platform that can be managed independently. However, having all virtualizations inside the same OSGi platform allows the use of common services as presented in Fig. 2.4.

Fig. 2.4 Virtualization use case

This figure shows a scenario where two service providers want to manage the service platform. Both users of the RGW will manage the lifecycle of the bundles installed that means since there is not root in the gateway, one provider can uninstall bundles of the other provider. The new model solves this problem providing a kind of virtualization. Each virtual platform created presents to the user an interface to manage the/his whole system as it would be the only authorized user.

The objective of virtualization is to add mechanisms to the OSGi platform that allow having different instances of the platform that can be managed independently.

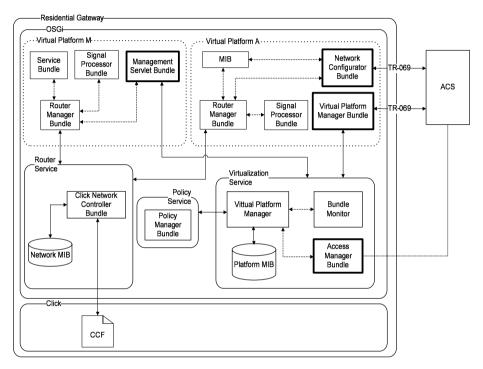

Fig. 2.5 Multi-provider functional block diagram in the RGW

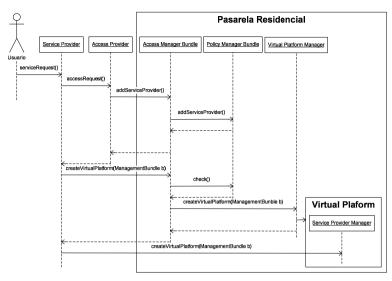

The "Virtualization service" is a set of bundles that manages all virtual platforms. It is in charge of creating new virtual platforms, managing the registration of local and global services (Virtual Platform Manager), monitoring (Bundle Monitor) the use of resources by bundles and providing a generic access agent (Access Manager Bundle) to allow external entities to create new virtual platforms. Permissions for creating virtual platforms and installed services are checked and managed dynamically in the "Policy Manager Bundle". This bundle is usually managed by the access provider.

In addition to the infrastructure for virtualization there are *virtual platforms*. Each one has its own bundles and services and its own manager agent. In case of Fig. 2.5 there are two virtual platforms, one of them

corresponds to the one presented in the mono-provider approach and uses two different Management Agents: "Network Configurator Bundle" and "Virtual Platform Manager Bundle". The Virtual Platform A is used to manage the router automatically with TR-069 protocol. The Virtual Platform M platform contains only one Management Agent, the "Management Servlet Bundle" which is a servlet for manual management of both, router and services. I.e. the bundles and services of the virtual platform and those which are not in the virtual platform but which have been installed by the provider.

This architecture implies four different kinds of users with different roles: One is the end user who will be enclosed in a virtual platform via a user interface. Furthermore, there is the system vendor user who will access to the RGW in order to upgrade the firmware. A third user is the access provider who defines the policies to access the RGW. Finally, the service providers only access to their virtual platform to manage their own services.

#### 2.4.3 Policy Management

Not all aspects of the management of the RGW by multiple users are covered by virtualization as is the case of the access to the services of a user by another user. In this case it is needed to establish a way of manage this issues out of the virtualization. Like other configuration issues it must have dynamic character due to dynamically added and deleted services and service provider. There are different aspects to be considered as management policies as the creation of virtual platforms.

When a service provider or an end user needs to create a virtual platform they have to be entitled to create it. In case of end users, a preconfigured virtual platform is provided by the RGW. This virtual platform owns bundles which provides and interface for the management of the RGW by the user. The task that this interface allows to do includes the creation of new end users and new virtual platforms for those users; it has the role of an administrator. In the case of service providers, the access provider has to allow the creation of the virtual platform as is shown in Fig. 2.6. The user hires a service from a service provider, then, this one sends a request for access to the access provider because he wants to configure the RGW and to allow the service provider to create a virtual platform. After that, the service provider can create a virtual platform installing his management. Via his management bundle he will install the service and he can configure the router.

Fig. 2.6 Sequence diagram for creating a virtual platform for a service provider

The control of consuming resources is another issue required and thus policies are needed. The bundle monitor checks the use of resources of the different bundles with the possibility of grouping it into virtual platform. It is possible to limit CPU resources, memory or bandwidth per virtual platform or bundle so if this limit is exceeded, a corrective action can be performed. These actions are: stop the bundle that is abusing of the resource, stop one of the bundles of a virtual platform or do nothing if the use the resources are not in a critical situation. The manger of the virtual platform is in charge of defining which bundle is candidate to be stopped in case the virtual platform exceeds the limit. The access provider rules the limits for the bandwidth. The end user defines all limits for the use of CPU or memory although these limits should be default ones.

A final issue to be managed by the Policy Manager Bundle is profiles of different end users and their rights to install services. This is configured by the end user *root*.

### 2.5 Results

A demo scenario has been developed to check the viability of the proposed model. The RGW has been implemented in an embedded PC with a CPU VIA C3 533MHz. The PC is running under Linux Ubuntu 6.06. J2SE 1.5 has been selected for the installation and development of the bundles. For the OSGi installation the distribution Oscar 1.5 [11] has been used and the

version 1.5 of the Click [12] software router has been selected. Also, two multimedia servers have been created to simulate different service providers.

The demo scenario has been implemented with all devices described. The access network has been simulated over an Ethernet network with injected traffic. In the home network scenario two laptops have been used as players of the multimedia content.

The complete functionality has been tested in a small case study. The results obtained confirm the functionality of the model and the implementation. It was possible to manage data flows and to change the QoS for the simulated multimedia services.

#### 2.6 Conclusions

This chapter presents a model for the management of a RGW in a multiprovider scenario. It is based on the virtualization of the service platform that runs in the RGW. This virtualization is enhanced by a management of policies and aspects as common resources management and access policies.

It provides service and device integration independently from any technology, and furthermore, it interconnects the home network to the access network. The model proved to provide the mentioned capabilities without imposing a restriction on the number of remote management units or service providers. The feature to provide policy management of the different resources has been realized via new services that have been added to the RGW platform. These services are sharing several infrastructural framework parts in order to keep the overall overhead low.

### 2.7 Future Work

One aspect of the future work will be dedicated to further modularize the virtual platform architecture and thus to provide a pool of features for a multi-provider concept derived from the current needs. A second part of the work is to integrate the virtual platform prototype into a gateway provided by network operators. It is assumed that several services can be omitted since not each RGW will need to provide the full set of functionalities contained in the proposed model. Finally, as a more ambitious way, it is planned to provide the needed functionality for a device connected to different access networks.

**Acknowledgment** This work has been partly supported by the Multi Service Access Everywhere (IST-Program; MUSE-IST 026442) [13] project that is an Information Society Technologies (IST) priority of The Sixth Framework Program (FP6) of the European research activities and by the PLANETS project [14] (MEDEA+ A306 funded by the Spanish Ministry of Industry; FIT-330220-2005-111), and finally, by the MEC I+D project InCare-FAMENET. Ref: TSI2006-13390-C02-02.

### References

- 1. K. Hofrichter, "The Residential Gateway as Service Platform". ICCE, International Conference on Consumer Electronics. Jun. 2001. ISBN: 0-7803-6622-0

- D. Waring, "Residential Gateway Architecture and Network Operations," International Organization for Standardization (ISO) and International Electrotechnical Commission (IEC) document: JTC 1/SC 25/WG 1 N 848, May 1999

- 3. Home Gateway Initiative, http://www.homegatewayinitiative.com, June 2008

- J.C. Dueñas, J.L. Ruiz and M. Santillán, "An End-to-End Service Provisioning Scenario for the Residential Environment", IEEE Communications Magazine, vol. 43, no. 9. Sep. 2005

- E. Cho, C. Moon, D. Park and D Baik, "An Effective Policy Management Framework Using RBAC model for Service Platform based on Components", Software Engineering Research, Management and Applications, 2006. Fourth International Conference on, (09–11), 281–288. Aug. 2006. ISBN: 0-76952-656-X

- Y. Royon, S. Frénot and F. Le Mouel, "Virtualization of Service Gateways in Multiprovider Environments", 9th International SIGSOFT Symposium on Component-Based Software Engineering (CBSE06), Stockholm (Sweden), Jun. 2006

- 7. Open Service Gateway Initiative (OSGi) Alliance. Jun. 2007. http://www.osgi.org

- 8. J.E. Smith and R. Nair, "Virtual Machines: versatile platforms for systems and processes", Elsevier, June 2005. ISBN: 1-55860-910-5

- 9. DSL Forum, "TR-069: CPE WAN Management Protocol", May 2004. http://www.dslforum.org/aboutdsl/Technical Reports/TR-069.pdf

- M. Ibañez, N. Martínez Madrid and R. Seepold, "An OSGI-based Model for Remote Management of Residential Gateways", LNCS: 10th Asia-Pacific Network Operations and Management Symposium, APNOMS 2007, Vol. 4773, Springer LNCS, ISSN: 0302-9743, 2007

- 11. Oscar OSGi platform, Jun. 2007. http://forge.objectweb.org/projects/oscar/

- 12. The Click router, Jun. 2007. http://www.pdos.lcs.mit.edu/click/

- Multi Service Access Everywhere (MUSE) European Project, MUSE-IST 026442. Jun. 2008. http://www.ist-muse.org/

- Platforms for Networked Service Delivery (PLANETS), MEDEA+ project A-121, mostly financed by the Spanish Ministry of Industry under project Num. FIT-330220-2005-111, Jun. 2008. http://www.medeaplus.org

# Chapter 3

# Embedding Multi-Task Address-Event-Representation Computation

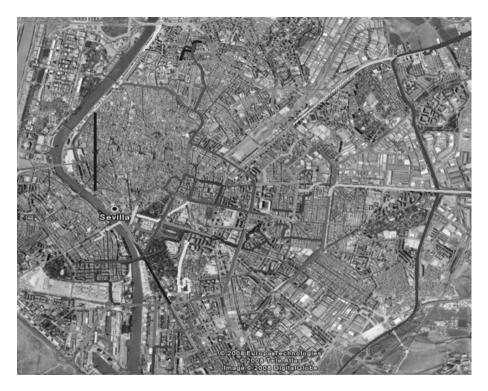

Carlos Luján-Martínez, Alejandro Linares-Barranco, Gabriel Jiménez and Antón Civit

Depatment Arquitectura y Tecnología de Computadores, Universidad de Sevilla, Sevilla, SPAIN, cdlujan@atc.us.es, alinares@atc.us.es, gaji@atc.us.es, civit@atc.us.es

Abstract Address-Event-Representation, AER, is a communication protocol that is intended to transfer neuronal spikes between bioinspired chips. There are several AER tools to help to develop and test AER based systems, which may consist of a hierarchical structure with several chips that transmit spikes among them in real-time, while performing some processing. Although these tools reach very high bandwidth at the AER communication level, they require the use of a personal computer to allow the higher level processing of the event information. We propose the use of an embedded platform based on a multi-task operating system to allow both, the AER communication and processing without the requirement of either a laptop or a computer. In this paper, we present and study the performance of an embedded multi-task AER tool, connecting and programming it for processing Address-Event information from a spiking generator.

Keywords Address-Event-Representation, AER tool, embedded AER computation.

### 3.1 Introduction

Living creatures are able to realize tasks that are not easily done by traditional computation systems. We can receive a huge amount of visual information, distinguish an object in motion, infer its future position and act on our muscles to take it in the order of milliseconds. Neuro-informatics aims to emulate how living beings process data. Efforts are being made in recent years by the research community [1] to develop VLSI chips that perform bio-inspired computation.

N. Martínez Madrid, R.E.D. Seepold (eds.), *Intelligent Technical Systems*, Lecture Notes in Electrical Engineering 38, DOI 978-1-4020-9823-9\_3, © Springer Science+Business Media B.V. 2009

Address-Event-Representation, AER, was proposed by the Mead lab in 1991 for communicating between neuromorphic chips with spikes [2]. There is a growing community of AER protocol users for bioinspired applications in vision, audition systems and robot control, as demonstrated by the success in the last years of the AER group at the Neuromorphic Engineering Workshop series [3]. The goal of this community is to build large multi-chip and multi-layer hierarchically structured systems capable of performing massively-parallel data-driven processing in real-time [4]. A deeper presentation of AER will take place in Section 3.2. These complex systems require interfaces to interconnect them and to connect them to PCs for debugging and/or high level processing. There is a set of AER tools based on reconfigurable hardware that can be connected to a computer. They achieve these purposes with a very high AER bandwidth but with the need of a PC for the higher level processing. A new philosophy was born at the last Workshop on Neuromorphic Engineering (Telluride, 2006) to improve this, which is based in the use of an embedded GNU/Linux system running over an embedded powerful microprocessor with network connectivity. This will let neuromorphic engineers to use AER standalone platforms for high level event processing when developing or building AER systems, to use it as a first test platform for hardware implementation of new algorithms and to implement complex algorithms of neuroinspired models which are not always easily portable to pure hardware solution, as learning algorithms, development of connectivity, etc.

We present in this chapter a microprocessor based solution, where the AER bus is connected directly to it by using its general purpose I/O ports, GPIO, as a first approach and in order to study the advisability of its use within AER based systems. We will solve the image reconstruction and edge extraction from event streams problems for this purpose, which requires a high AER bandwidth when no preprocessing is done and will let evaluate the performance of the embedded system. Also, we have compared the proposed solution with other hardware solutions and other multi-task approaches.

#### **3.2** Address-Event-Representation

Figure 3.1 shows the principle behind the AER. Each time a cell on a sender device generates a spike, it communicates with the array periphery. A digital word representing a code or address for that cell is placed then on the external inter-chip digital bus, the AER bus. This word is called event. Additional handshaking lines, Acknowledge and Request, are used for completing the asynchronous communication. In the receiver chip, the spikes or events are guided to the cells whose code or address appeared on

the bus. In this way, cells with the same address in the emitter and receiver chips are virtually connected by streams of spikes. These spikes can be used to communicate analog information using a rate code, by relating the analog information to the time between two spikes that correspond to the same neuron, although this is not a requirement. More active cells access the bus more frequently than those that are less active. The use of arbitration circuits usually ensures that cells do not access the bus simultaneously. These AER circuits are generally built using self-timed asynchronous logic [5].

Fig. 3.1 Rate-coded AER inter-chip communication scheme

In general, AER is useful for multistage processing systems, in which as events are generated at the front end they travel and are processed down the whole chain (without waiting to finish processing each frame). Also, in multistage systems, information is reduced after each stage, thus reducing the event traffic. A design of a neuromorphic vision system totally based on AER has taken place under the European IST project CAVIAR, "Convolution Address-Event-Representation (AER) Vision Architecture for Real-Time" (IST- 2001-34124) [1]. This chain is composed by a 64×64 retina that spikes with temporal and contrast changes [9], two convolution chips to detect a ball at different distances from the retina [6], an object chip to filter the convolution activity [7] and a learning stage composed by two chips: delay line and learning [8]. The maximum throughput rate takes place at the output of the silicon retina. Although it is able to emit 4Mevents/s, real applications, such as someone walking along a corridor or even the beat of an insect wing, vary from 8 to 150 Kevents/s [9], respectively. These values will be used further for comparing the results with real applications (cf. Table 3.1).

Table 3.1 Event Rate for some previous AER-tools. The communication to or from the PC is done by the PCI bus or the USB protocol. They achieve a very high AER bandwidth but with the need of a PC for the higher level processing

|               | e ingiter rever processing | 2              |             |

|---------------|----------------------------|----------------|-------------|

| AER-tool name | Event rate                 | AER-tool name  | Event rate  |

| Rome PCI-AER  | 1 Mevents/s                | CAVIAR PCI-AER | 8 Mevents/s |

| USB-AER       | 25 Mevents/s               | USB2AER        | 5 Mevents/s |

| mini USB-AER  | 300 Kevents/s              |                |             |

The research community is also working on applying these systems to different actuators [10–13], from translating AER information into actuator control information (e.g. PWM and PFM) to developing hybrid systems, bioinspired sensors for acquiring preprocessed data and classical computation for decision and control. This hybrid scheme is successfully being applied to other fields, such as sensor networks [14,15].

#### **3.3** Spike Processing Over Multi-Task

Generally, buffers of event streams are prepared on the PC [16], and sent via these AER-tools to the AER bus or an obtained event stream is sent to a PC and a high level processing is done then, such as learning algorithms for the VLSI neuronal network, development of connectivity, models of orientation selectivity, which are not always easily portable to pure hardware solutions [17,18]. Let us present two significant approaches/examples of multi-task spike processing and highlight aspects to bear in mind when translating to an embedded platform.

The first one is interesting because it covers PCI connection and high level spike processing over a GNU/Linux operating system. A hardware/software framework for real-time spiking systems was proposed in [17]. Rome PCI-AER [3] is connected to a Pentium IV at 2.4 GHz running a GNU/Linux 2.4.26 desktop distribution. The software architecture consists on kernel code, module, for controlling this AER hardware interface, an UDP server of event buffers, called monitor, and one or more clients for high level spike processing, called agents. The monitor is implemented in C++ and agents could be implemented in other languages, such as Matlab. It presents a maximum event rate of 310 Kevents/s without high level spike processing.

This second approach covers USB connection to the PC and actuator control at a hybrid processing system under Microsoft Windows XP operating system. Delbruck [13] presents a hybrid system for fast motor control. A single-axis arm acts as goalkeeper and is able to block 80–90% of balls that are shot with >150 ms time to impact. A silicon retina, bioinspired, acts as visual sensor [19]. Spikes are collected by a USB2AER board [20] and sent to a PC, a 2.1 GHz Pentium M laptop, over USB. Data is processed, procedural computation, by a Java application over Microsoft Windows XP operating system and the result is sent over USB full-speed to a motor control board based on C8051F320 MCU, which acts on the single-axis arm. There are three threads: high priority one for reading events from USB, highest priority one for writing motor control decision information to the USB motor control board and one for visualizing the scene and GUI. Each

ball generates 30 Kevents/s as mean value, which means an USB Bulk transfer of 128 events every 4 ms.

On both approaches, powerful PCs are used, so it is not possible to implement their systems as embedded standalone ones. Also, complex and efficient processor architectures are used. Embedded systems do not have so resources. On the first approach, there is a data and time overhead from the UDP/IP protocol architecture, even if loop-back network interface is used. It would be desirable to avoid it due to the resource limitations of embedded systems. The second approach runs on JVM which introduces instruction overhead and reduces the performance. Although only some part of the application is running purely on it, byte codes have to interpreted and corresponding processor instructions have to be executed, garbage collector may execute periodically, etc. Once more, the use of JVM should be avoided to get a better performance on an embedded system.

### 3.4 Embedding Multi-Task Spike Processing

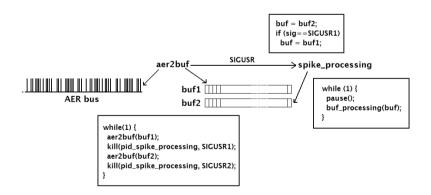

We propose the use of Intel XScale PXA255 processor running an embedded GNU/Linux 2.6 system using uClibc and double-buffering signaled exchange scheme for receiving and processing AER information.

## 3.4.1 Hardware Architecture

The Intel XScale core [21] is an ARM V5TE compliant microprocessor and provides the ARM V5E DSP extensions, although it does not provide hardware support for floating point instructions. It is a 7-stage integer/8-stage memory super-pipelined core. The core presents a Multiply/Accumulate unit, MAC unit, that supports early termination of multiplies/accumulates in two cycles and can sustain a throughput of a MAC operation every cycle. Also, it offers 32 KB of data cache, 32 KB of instructions cache and an MMU. The ability to continue instruction execution even while the data cache is retrieving data from external memory, a write buffer, write-back caching, various data cache allocation policies which can be configured different for each application and cache locking improve the efficiency of the memory bus external to the core. In addition, a Branch Target Buffer is present, that holds 128 entries with a miss predicted branch latency penalty of 4 core cycles and 0 when predicted correctly. The processor has 84 GPIOs that can be programmed to work as function units to manage serial ports, I2C, PWM, LCD, USB client 1.1, etc. In addition, platform will need RAM, Flash memory and network connectivity.

#### 3.4.2 System Software Architecture

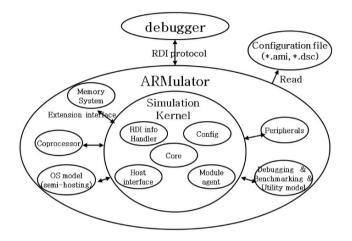

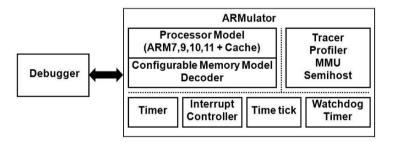

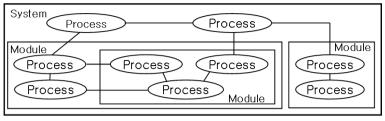

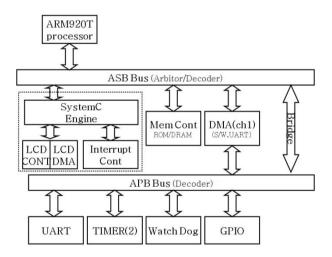

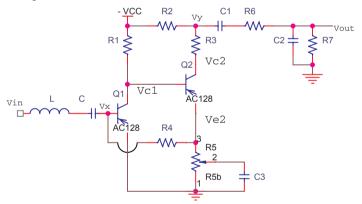

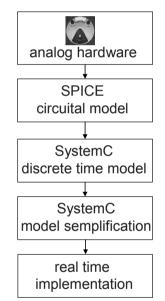

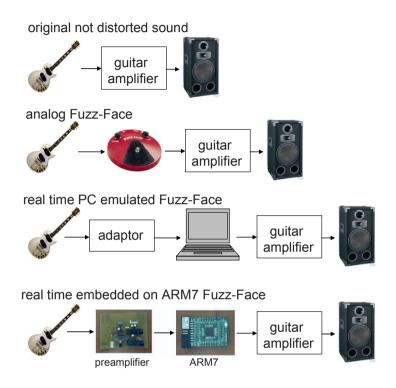

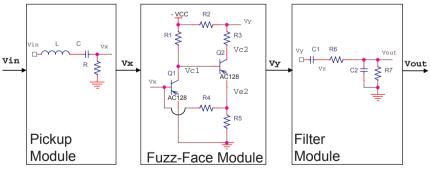

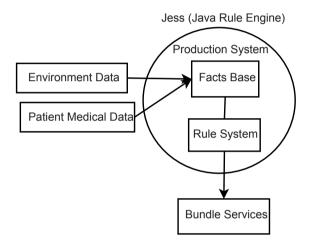

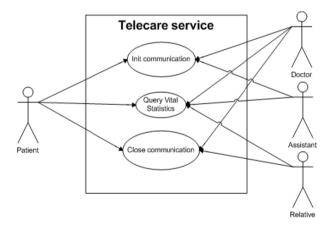

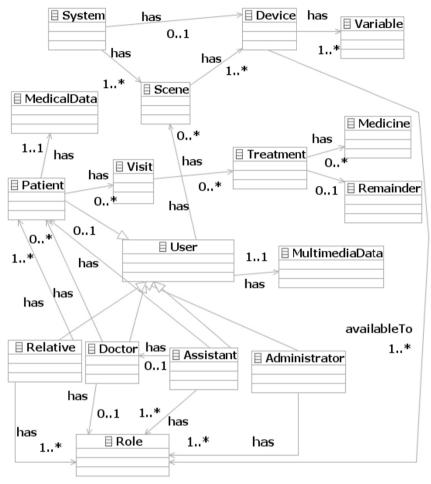

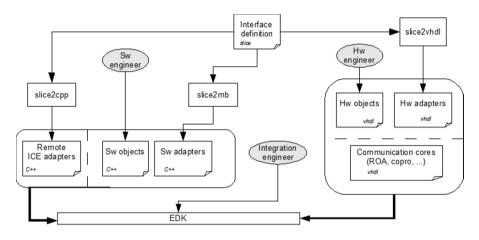

uClibc is a lightweight and widely used library for developing embedded Linux systems, which supports shared libraries and threading. This lets the application's binaries to be lighter and allows running on tiny hardware systems. GNU/Linux is a multi-task general purpose operating system, so it is designed for obtaining a good mean performance. So, it needs to be adapted for AER computing.