For Timothy

# **Practical Design of Digital Circuits**

**Basic Logic to Microprocessors**

Ian Kampel, C.Eng., M.I.E.R.E.

**Newnes Technical Books**

#### Newnes Technical Books

is an imprint of the Butterworth Group which has principal offices in London, Boston, Durban, Singapore, Sydney, Toronto, Wellington

First published 1983

© I. J. Kampel, 1983

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, including photocopying and recording, without the written permission of the copyright holder, application for which should be addressed to the Publishers. Such written permission must also be obtained before any part of this publication is stored in a retrieval system of any nature.

This book is sold subject to the Standard Conditions of Sale of Net Books and may not be re-sold in the UK below the net price given by the Publishers in their current price list.

#### British Library Cataloguing in Publication Data

Kampel, Ian Practical design of digital circuits 1. Digital integrated circuits I. Title 621.381'73 TK7874

ISBN 0-408-01183-1

Typeset by Butterworths Litho Preparation Department Printed in England by Whitstable Litho Ltd, Whitstable, Kent

### Preface

As the title of this book suggests, the aim of this work is to demonstrate the *practical* aspects of digital circuit design. For this reason the amount of pure theory has been kept to an absolute minimum and the primary objective has been one of showing the reader the most direct route to 'thinking' about digital design in the manner of an experienced designer. The intention is to give the reader sufficient confidence to embark upon his own design projects utilising digital integrated circuits as soon as possible.

The word *practical* is emphasised, for there can be quite a gap between a practical design approach and a purely theoretical one. Most courses on digital electronics spend quite a considerable time describing how particular integrated circuits function internally. There is no need for the designer to know this, for he uses them as 'black boxes'. There is also a tendency to over emphasise techniques for minimising logic networks in order to achieve the minimum number of gates. These make good academic exercises and allow the student to really get to know Boolean algebra and Karnaugh maps, but they do not reflect the true design environment where low component count and cost minimisation are the most important factors. The minimum number of *used gates* does not automatically give the minimum number of *devices*, and is unlikely to do so where many different types are demanded. All the former may lead to is an unreasonable number of under-utilised devices.

Minimising – or simplifying – one logic network to produce another with less gates also assumes that you are starting with a wasteful network in the first place. Since good design practice should not create such a situation, this is rather like concentrating on how to compensate for shortcomings rather than how to avoid them. The experienced designer always has certain good design principles in mind when he sets about designing a digital circuit, and the purpose of this book is to show what these are.

For those having a reasonable familiarity with linear design but no knowledge of digital design, I would like to assure them that digital design should present them with few problems once they get some 'hands-on' experience. For a digital design is far easier to analyse on paper than a linear design. It is always possible to overlook an important factor or parameter in a complex linear design, but with careful thought, it should always be possible to complete a digital design with a much higher degree of confidence. It is a reasonable proposition to consider all possible conditions within a digital circuit, but such may not be the case for a linear circuit.

There is no doubt about it that digital electronics is here to stay. With the advent of the microprocessor its future is assured, and since any microprocessor needs to interface with fairly conventional digital devices, there will always be a call for digital design engineers. As the range of components increases year by year, and as the price of such components continues to stay at reasonable rates – or even drops – despite ever present inflation, more and more equipment is likely to go digital. There will always be the need for linear circuitry where any form of input or output transducer is concerned, but the system designer is finding it more efficient, cost-effective, and reliable to convert to or from digital circuitry at the earliest opportunity. In complex systems his aim will be to convert from digital circuitry to or from microprocessor software at the earliest opportunity as well.

This book concentrates on digital design techniques using the basic building blocks of such circuits. These devices will always be around simply because they are so basic. Even allowing for the most sophisticated microprocessors of the future, any particular system inevitably has its own particular input/output interface problems, and these devices will always be needed for such purposes. Therefore despite the rapid advancement in microelectronics and in microprocessor technology, I am confident that the techniques described in this book will remain relevant for the foreseeable future.

This book is aimed at a fairly broad market: it is intended to aid the linear design engineer to cross the barrier into digital electronics; it should provide interesting supporting reading for students studying digital electronics from the more academic viewpoint; it should enable the enthusiast to design much more ambitious and sophisticated projects than he could otherwise attempt if restricted to linear devices. The great advantage that digital circuitry can offer is high reliability, and this should be the ultimate aim of any electronics designer.

My own background is in both linear and digital design, and my current occupation involves me in many large and complex systems designed by a wide variety of manufacturers. This viewpoint is a useful one in observing current trends, and one that is reflected in the pages to follow.

You cannot learn faster about anything than by becoming personally involved. My recommendation to the aspiring digital designer is to read through this book in order to get an idea of how to go about designing digital circuits – be they large or small – and then to have a go at a simple design straight away. Electronic games provide an ideal excuse for such an exercise, and digital electronics can provide reasonable sophistication at moderate cost and with minimal complexity. Here is an ideal proving ground.

Good luck!

I.J.K.

### Acknowledgements

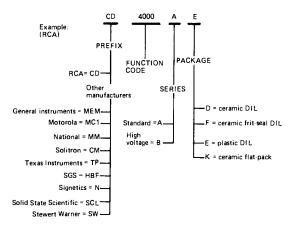

The author is indebted to the staff of Texas Instruments and RCA for their kind permission to reproduce certain illustrations relating to their products. He would also like to extend his particular thanks to RCA for validating material relating to the 'COSMAC' micro-processor.

### Using this book

This book is intended to be read in the order presented: it then offers the reader a course in the *practical design of digital circuits*. Like any other course, it is necessary to introduce new concepts gradually, and to start with basics and to gradually advance to more and more complexity as the student progresses. Thus the book cannot be effective unless read in this manner; random dipping into later chapters may do no more than give the impression of greater difficulty than should otherwise be experienced.

There are many books on digital electronics, but very few on the techniques of digital design. This is probably because any form of design is essentially creative, and it is always difficult to teach creativity. This does not mean that it is impossible. For example, it is possible to teach someone the basic principles of painting, but once they have learned these, the field is wide open for them to express themselves in their own particular and individual way. The same applies with digital design.

Part 1 of this book teaches the basic principles of practical design, and introduces the designer to his 'tools' – or rather, the range of devices he has to call upon. Part 2 shows him how to put these together into viable designs. The only way to learn how to design is to study how others approach it, and then to have a go for yourself. For this reason, Part 2 of the book includes two detailed descriptions of actual design exercises. The first of these is an exercise in CMOS design, and is fairly simple. The second is a much more complex design for an electronic game, using TTL devices. The reader is urged to keep studying these design examples until he fully understands them. Once he reaches this stage, he may progress towards his own designs with confidence.

A book on digital design would not be complete today without some coverage of microprocessors. Microprocessors represent a further stage of advancement in terms of technology, and the modern tendency is to replace special-to-purpose digital circuitry by microprocessors wherever possible. Since all microprocessors have their special features, it is impossible to adequately cover the subject in one section of this book – or even in one entire book. Each microprocessor is worthy of one or more books to itself! What this book does do, however, is to provide sufficient information about microprocessors for the reader to appreciate their advantages or disadvantages, as the case may be. The application and the circumstances dictate whether a particular design is best suited to ordinary logic or to a microprocessor.

The book culminates in a practical illustration of how a particular design problem changes emphasis when a microprocessor is introduced, by reflecting on how the electronic game discussed in Part 2 might have been tackled using a microprocessor.

This book has to cover a vast amount of ground as efficiently as possible. This has been achieved by careful integration of subject matter within the text. The main text is supported by various appendices at the rear of the book, and these provide the aspiring designer with abridged design data, in order to get him off the ground without further expense or delay. It is strongly recommended, however, that the reader purchase a good data book on digital devices as soon as possible. Perhaps the best source of TTL data is: 'The TTL Data Book for Design Engineers', published by Texas Instruments. Such a wide selection of devices can be rather confusing – and daunting – therefore the appendices to this book do reduce the problem to a manageable level during the learning process.

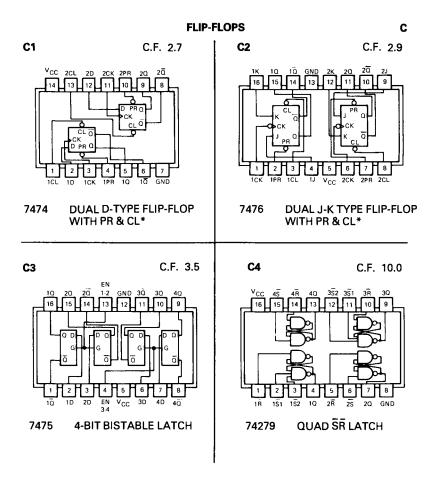

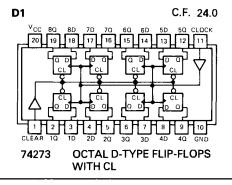

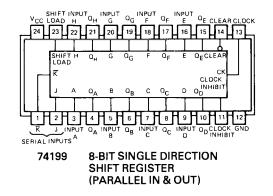

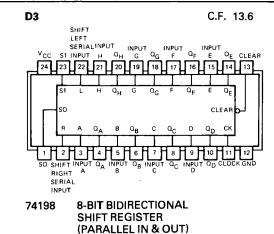

The abbreviation 'App. C2' – or similar – is to be found throughout the text. This refers to entries in Appendix A, and guides the reader to device data. In the example given, 'App. C2' refers to the 7476 device, reference C2 on page 274. No text references are made directly to any of the other appendices, unless specified in full.

The logic symbols used throughout this book comply with MIL-806B standards. This choice has been made because engineers recognise these symbols worldwide, and these are the symbols most frequently found in manufacturer's data. Further information on drawing standards is to be found within Appendix E, together with an explanation of why the MIL standard has been chosen rather than a more recent standard. This appendix also contains equivalent symbols for various gates. It is worthwhile adding that the MIL standard symbols are also much more popular with engineers in general, and do have a great advantage over the more recent rectangular symbols for the purposes of this book: they require far less explanation and are easier for the novice – and engineer (sic!) – to understand.

Everyone knows that this is the age of the silicon chip. If you are interested in electronics, then you will want to come to grips with it as soon as possible. The aim of this book is to place it within your *practical* grasp.

# Part 1 – Basic logic

Give us the tools, and we will finish the job. Sir Winston Churchill (1874–1965).

# 1 The ubiquitous silicon chip

It does not seem long ago that the word 'transistor' was bandied around by all and sundry as the description for a transistor radio. It was not generally appreciated then that a 'transistor' was merely one component within such a device. In a similar manner the media has now latched onto the phrase 'silicon chip' to describe anything which is electronic, rather sophisticated, and contains *any* sort of semiconducting device. Since this word has only really been discovered by the masses since the advent of the microprocessor, the phrase tends to be used synonymously with the word 'microprocessor'. Once again the wrong image has been created, for the 'silicon chip' has been around for a great deal longer than the microprocessor.

The first switching circuits which were the forerunners of modern digital circuits were formed from discrete components such as transistors and diodes. These were all very well for simple circuits, but they very quickly became large and unwieldy as soon as the logic began to get complicated. This ushered in the *integrated circuit* which incorporated several devices onto a single chip. This was the birth of the silicon chip.

By this time the techniques of fabricating silicon planar devices were well understood and it was possible to produce large quantities of reliable silicon transistors. The usual practice was to manufacture a large number of discrete transistors on a single chip, so it was a natural development to manufacture simple transistor circuits onto a single chip instead. Passive components such as resistors or small value capacitors could equally well be incorporated into the circuits. Such devices were subsequently referred to as *Small Scale Integration* (SSI) devices, and these still form the basis of simple logic gates today.

As digital circuitry gained ground there came the need for set circuit configurations to be repeated more and more often. Particular arrangements of gates form the building blocks of digital circuits, and in order to improve system reliability, minimise the number of interconnections concerned, and to miniaturise the circuitry involved, *Medium Scale Integration* (MSI) devices were born.

The basis of such circuits was a fairly basic switching transistor, although improvements such as Schottky clamping diodes were introduced to improve switching speed. The transistor does require a fairly large area in microelectronic terms, and it was found that the metal oxide silicon field effect transistor (MOSFET) could be fabricated in much smaller areas, allowing thousands of transistors and resistors to be packed into one tiny chip area. Inevitably these high density circuits came to be known as *Large Scale Integration* (LSI).

The particular requirements of different systems demands different predominant features such as high speed, low power, or simply a compromise between the two, for these features do tend to conflict. The most common devices at present are formed from conventional transistors and are known as transistor transistor logic (TTL) because of their form of interconnected transistors. The speed of these is adequate for most applications but the power consumption does require mains originated supplies unless the component count is quite small. Schottky barrier diodes are used in conjunction with certain families of these TTL circuits to prevent the transistors saturating, and thereby increases their switching speed, but the current consumption is still a problem. MOSFET devices get over the problem of power consumption, but these have the disadvantage of being comparatively slow and of also being somewhat prone to damage due to electrostatic charge if they are mishandled.

More will be said about the various families of devices in a later chapter, but it will be seen that there are several different families to choose from according to the designer's needs. For most applications the designer will choose conventional TTL devices which compromise between speed and cost. It is these devices that we shall chiefly be concerned with in this part of the book. Apart from current levels and switching speeds, and also the available power supply range, there is no functional difference between these various families so far as their logical significance is concerned. For this reason we shall concentrate upon logic functions before introducing the confusion of family variants.

This brief review of the development of the ubiquitous silicon chip cannot be complete without considering the latest innovation: the microprocessor. The sophistication of conventional integrated circuits brought about computers of modest proportions compared with the first valve efforts, and even great improvements over the early transistor versions, but the microprocessor was the greatest step forward of all. It came about as a result of the expertise which developed in the production of LSI circuits, and it was inevitable that the end result would be a computer on a chip: for this is really what a microprocessor is.

The main differences between a microprocessor and a conventional computer are speed and computing capability; the computer wins on both counts. A computer operates with *data words* comprising a set number of *bits*. A *bit* represents the smallest single piece of digital data, and it can indicate either one of two logic states. The most common powerful computers operate with 24-bit words. Microprocessors are most commonly arranged to handle only 8-bit data words. This fact, combined with lower operating speeds, is the main reason why computers are not immediately threatened by their smaller brethren. Computers use faster devices.

We have seen tremendous advances in microelectronics over the past decade. Already 16-bit microprocessors are a reality, and 24-bit microprocessors can only be over the horizon. That only then leaves us with the speed limitation, but modern innovation should find a way round that. Already it is quite common to use several microprocessors in a single system, and it is not inconceivable that several microprocessing elements might be interconnected on a single chip to provide means of carrying out parallel processing in such a manner that the speed limitations of the material might be compensated for. This is only speculation, but it does remind us that we are by no means at the end of the road just yet. A faster material might even be discovered!

Just because microprocessors are versatile, this is not sufficient justification alone for incorporating them into a given system. If the system would require a tremendous amount of conventional logic then there is obviously justification for a computer or microprocessor, but for smaller systems and less demanding applications, a microprocessor might not be the most cost-effective solution. For every microprocessor requires supporting software, and software takes time to write and debug. In commercial terms this can prove to be very costly in a development program, and unless the volume of subsequent sales can justify it, then conventional logic might be a better bet.

The size of a system is not the only deciding factor: rather, it is the cost of software development. Time is of little significance to the hobbyist, for example. Therefore the microprocessor does offer *him* the means of designing some very sophisticated systems which have relatively low costs in hardware terms. Microprocessors can be purchased very cheaply now.

It will be seen that the development of modern electronics has led to three discrete areas of technology: linear electronics, digital electronics, and now software, the latter forming an integral part with the innovation of the microprocessor.

The innovation of digital electronics led to specialist designers and placed a technological barrier between two different branches of hardware design. Computer technology allowed mathematicallyminded programmers to program computers with no real knowledge of computer hardware, and hardware engineers were able to work on computer hardware with little real knowledge of software. The microprocessor brought an end to this cosy situation, for it is essentially a digital device and needs to be built into a digital circuit.

A microprocessor system raises the question of how much should be handled by the software and how much by the hardware, and the solution to this hardware-software trade-off can only adequately be answered by someone able to understand both. It has led to a new kind of engineer: a *microprocessor engineer*.

All this may sound rather formidable, but it need not be so if grass roots are returned to and the history of the silicon chip is remembered. For digital electronics is no more than a *restricted* branch of linear electronics. Circuit performance is more predictable because we are only dealing with circuits which switch between two voltage levels: high or low. The microprocessor is only a special kind of digital integrated circuit. True, it does require supporting software, but even here there are different levels at which it may be approached. At the lowest level there is machine code, where specified codes produce particular hardware manipulations, and this is no more frightening than the function of any other LSI device. At the next level there are programming languages such as BASIC, which as the name suggests, is very easy to understand.

It would be a difficult task for a mathematician to get to grips with digital design unless he had some understanding of electronics, but it is an easy task for him to understand programming. Anyone capable of undertaking hardware design can fairly soon pick up microprocessor programming. Equally, anyone familiar with linear design can soon pick up the principles of digital design. Clearly they cannot expect to become instant experts, for any new technology takes time, but it is hoped that this assurance might spur on any doubtful linear designers. My belief is that it is an easier path for a linear design engineer to become an *effective* microprocessor engineer than it would be for a programmer with no electronics experience: for only he can see any electronic short-cuts.

This is the history of the silicon chip. It has had a spectacular past and has an assured future. Without a doubt it will have drastic changes on our life-style over the coming years and it is up to us to see that it is a change for the better. It can be. If we can show just a small proportion of the versatility and innovation that the physicists who have developed it have shown, the silicon chip can release man from a great deal of drudgery, and give him the time for more worthwhile pursuits. After such development, this is surely the only logical conclusion.

# 2 From linear to digital electronics

Digital electronics tends to *sound* much more sophisticated than linear electronics, and the very *sound* of it is sometimes enough to put off many otherwise very competent designers. Linear designers will sometimes produce very elaborate designs to achieve what amounts to a simple logic function; had they familiarity with digital electronics as well, that same requirement might have needed no more than a small number of digital integrated circuits (ICs). The aim of this chapter is to show that the barrier between the two technologies is little more than a 'sound barrier', and to emphasise that the way to approach digital design from a background of linear design is to regard it as a restricted form of linear electronics. It is because of these restrictions that it has been possible to introduce special symbols to represent repeatedly used circuit blocks. Once this has been truly appreciated, the mystique of digital electronics should be removed.

#### Simple diode logic

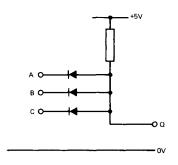

In order to understand the basic principles of logic, there is no better place to start than with the simplest logic circuits possible. Diodes give us the essential features of a logic gate, as illustrated in Figure 2.1. This shows three diodes connected to a common pull-up resistor tied to +5V. A, B and C are the circuit inputs, and Q is the output.

If all the inputs are taken to the supply rail of +5V (i.e. *high*), no potential difference occurs across any of the diodes, therefore no current flows through the resistor; as a consequence, the output Q is also high. If any of the inputs is taken to 0V (i.e. *low*), the diode in series with this input is forward-biased, and current flows through the resistor. Assuming a silicon diode with a forward voltage drop of nominally 0.7 V, this has the effect of pulling the output Q down to approximately +0.7V.

It does not matter if more than one input is taken low, for in this situation the diodes with grounded cathodes simply share the current which is limited by the resistor. *This is a simple logic gate*.

Logic circuits (or gates) are so named because they are capable of representing logic conditions. The above circuit represents the logic condition described by the following statement: A AND B AND C true gives Q true. If we separate the input conditions from the output by the equivalence sign, and replace the 'AND' statements by the shorthand notation of a dot, the above logical statement can be rewritten as follows:

#### A.B.C = Q

Because of the logical significance of this circuit it may be referred to as an 'AND' gate. In practice, a circuit as simple as this would not be used, but it does show the basic concept of digital logic, where only two signal levels are considered: either high or low. Digital circuits do not employ voltage levels between the conditions described as high or low, hence my earlier description of digital electronics as a restricted form of linear electronics.

Logical statements are expressed in the form of terms which may be either *true* or *false*. Given two possible conditions to represent electronically, we require only two voltage levels, hence the high/low circuit conditions. This only leaves us with one permutation to consider: which level represents what? From the logical point of view the choice is purely arbitrary, and both systems are employed. This has given rise to two logic conventions: *positive logic* and *negative logic*. The positive logic convention represents the true condition by the more positive voltage, whereas the negative logic convention represents the true condition by the more negative voltage; this is therefore easy to remember.

Because logic circuits represent only two different states, all arithmetic processes are carried out in *binary arithmetic*, which uses only the numbers 0 and 1. Logical statements are also described in terms of 0 for false, and 1 for true. Thus a logic 1 is the more positive voltage in positive logic, or the more negative voltage in negative logic. If the concept of positive or negative logic is confusing, not to worry! Most modern designs employ only positive logic, therefore to avoid confusion, this book only considers positive logic.

#### The transistor in logic circuits

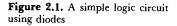

Logic requires both true and false conditions to be easily represented. False logic terms are represented by placing a bar over the term, e.g.  $\overline{Q}$ , pronounced 'bar-queue'. In electronic terms,  $\overline{Q}$  is simply the *inverse* of Q; thus if Q is high,  $\overline{Q}$  must be low, and if Q is low,  $\overline{Q}$  must be high. Obviously an inverter is therefore an essential requisite of logic circuits, and the reason why transistors play an important role. Consider now the circuit shown in Figure 2.2: this is basically the diode logic circuit previously discussed, but followed by a transistor inverter stage. This is a diode transistor logic (DTL) gate.

Figure 2.2. A diode transistor logic (DTL) gate

The introduction of transistors gives us an immense improvement, both logically and electrically. Logically, it provides the means of inverting or *complementing* a term (e.g.  $\overline{Q}$  is the complement of Q); without this facility, all logic conditions could not be represented. Electrically, the transistor has two advantages: it provides a buffer, enabling more inputs to be connected to an output (known as 'fanout'), and by providing all gate outputs with a transistor stage, it gives a wider voltage swing between logic levels. Where a silicon diode can only give a low level of +0.7 V, a silicon transistor in the *bottomed* condition (i.e. driven hard on by sufficient base current) can present a low level of around +0.2 V.

The circuit shown in Figure 2.2 is logically the same as that shown in Figure 2.1, except that the output is inverted by the transistor. If all the inputs are high, no current flows through any of the input diodes, which allows current to flow through what now becomes the base resistor, thereby biasing the transistor hard on, and producing a low at the Q output.\* If one or more of the inputs is taken to 0V, current flows through the base resistor and diverts to flow through the input diode/s. The two diodes in series with the transistor base ensures that the transistor is cut off with a potential of only +0.7V at the input resistor-diode junction, therefore the Q output is high.

The logic condition represented by the gate shown in Figure 2.2 can be expressed as follows:

#### $\overline{\mathbf{A}.\mathbf{B}.\mathbf{C}} = \mathbf{Q}$

This is read as: 'NOT (A AND B AND C) gives Q'. To interpret the expression, ignore the bar initially, and note the AND condition which applies to A AND B AND C; finally take the bar into account, which signifies an inverse form. Thus Q is *low* for the input condition A.B.C. Because the bar signifies 'NOT', this gate might be called a not-AND; in fact this is abbreviated to 'NAND'.

This form of diode transistor logic was the type of gate used in early SSI components. Note that the circle around the transistor has been omitted in order to distinguish this from a discrete transistor encapsulation, because the entire circuit is formed on a single integrated circuit. The next stage in the development of logic circuits was to introduce a new kind of multi-emitter transistor, thereby minimising the number of chip interconnections, saving space, and simplifying the manufacturing requirements. Because the input diodes were replaced by transistors, these devices became known as transistor transistor logic, or as we shall refer to them hereafter: 'TTL'.

#### The TTL gate

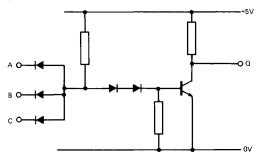

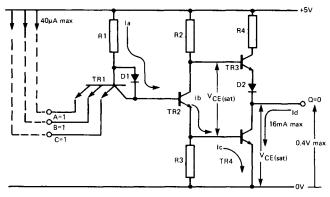

By diffusing a number of separate emitter n-types into the base p-type of the input transistor shown as TR1 in Figure 2.3, the same logic inputs can be derived within a single transistor. The diode D1 is a 'distributed' diode, but it is shown as a separate diode in this circuit in order that the operation may be better understood. This

<sup>\*</sup> In order to ensure that a transistor is bottomed, the base current must be at least as high as the maximum collector current divided by the d.c. current gain of the transistor in the bottomed state. Whilst modern silicon transistors can achieve current gains of 100–800 when not saturated, this figure is dramatically less when the saturated (or bottomed) condition is reached; figures of 10-20 are typical. Thus the maximum base resistance must be the collector resistance multiplied by the maximum current gain; a factor of  $\times 10$  is a good rule of thumb.

figure shows input C connected to 0V, and therefore at logic 0, and the inputs A and B connected to +5V, and therefore at logic 1. Only a negligible leakage current flows into A and B since these are reverse-biased diodes, but current I<sub>b</sub> flows out of the emitter connected to input C. This current is derived from the base current plus the larger current I<sub>a</sub>, flowing through R1 and D1. The input transistor bottoms as a result of this current and the collector of TR1 is at about +0.2V, i.e. the saturation level for the collector-emitter.

Figure 2.3. A TTL gate with one input low

Figure 2.4. A TTL gate with all inputs high

This condition cuts off TR2 and allows current  $I_c$  to flow through R2, so biasing TR3 into conduction, and allowing the larger emitter current  $I_d$  to flow through D2 and *out* at Q. This causes Q to be high, i.e. at logic 1. The characteristics of the standard 7400 series of TTL gates specifies that the maximum high level current which can be

drawn from the output  $(I_{OH})$  is 400 µA. Since the maximum high level input current  $(I_{IH})$  for any gate connected to an output is specified at 40 µA, this allows up to ten input gates to be connected to an output. The output voltage level in the high state  $(V_{OH})$  is specified as +2.4V minimum, which means that a logic 1 output should always be equal to or greater than this voltage.

Figure 2.4 shows the same gate with all the inputs high. Now no current flows out of the emitters of TR1, and the current  $I_a$  diverts to form the base current of TR2. Emitter current  $I_b$ , comprising both  $I_a$  and current drawn through TR2 collector, flows as base current  $I_c$  through TR4. This causes TR4 to switch hard on, and current  $I_d$  flows *into* the output Q. The transistor bottoms to give an output voltage equal to  $V_{CE(sat)}$  for TR4, thereby producing a logic 0. With TR2 bottomed in this condition, diode D2 ensures that TR3 is cut off.

The characteristics of the 7400 series gates in this condition specify that the maximum low level output current  $(I_{OL})$  is 16mA. Since the maximum low level input current  $(I_{IL})$  for any gates connected to an output is 1.6mA, this allows up to ten gates to be connected to any output. Thus for any logic conditions, this series of devices allows what is termed as *fanout* of ten, i.e. ten inputs may be connected to any output. The specifications also state that the maximum low level output voltage  $(V_{OL})$  shall be +0.4 V.

One characteristic worth bearing in mind is that whilst multiemitter transistors provide a load for each emitter in the high state, they do not do so in the low state. Thus if several inputs to the same logic gate are tied together, they only appear as a single low level load to the driving gate, since the current flowing out of the inputs is simply shared between the various emitters. In the high state each separate junction contributes its own leakage current. This is worth remembering, for unused inputs on gates can often be conveniently tied to neighbouring inputs. All inputs should be taken either high or low.

#### **Noise margins**

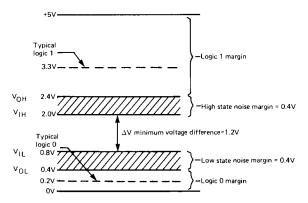

So far the output voltage levels have been discussed, but in order to provide safety margins within the specifications, the input requirements are made to overlap the output guaranteed levels to provide a noise margin of at least 0.4 V. Figure 2.5 depicts the noise margins.

The output high level is guaranteed to be at least +2.4V, but input gates accept a logic l above +2.0V to provide a high state noise margin of 0.4V. The output low level is guaranteed to be

Figure 2.5. TTL noise margins

+0.4 V or less, but input gates accept a logic 0 below +0.8 V, again ensuring a low state noise margin of 0.4 V. The minimum voltage difference between logic states must therefore be at least 1.2 V, and typical logic 1 and logic 0 levels are +3.3 V and +0.2 V respectively.

# 3 Logic gates

The previous chapter described a typical TTL gate in terms of its linear components. The gate shown in Figures 2.3 and 2.4 is a 3-input NAND gate. Like other gates in this family the output consists of a *totem-pole* arrangement with two output transistors. This ensures that a low impedance current source can be maintained in either logic state, and that adequate loading can be achieved with minimum risk of noise interference.

Having shown the typical internal structure of a basic gate in order to bridge the gap between linear and digital electronics, we shall now only consider logic *gates* as functional blocks. The background knowledge of how inputs and outputs are implemented is of value, however, in understanding device characteristics.

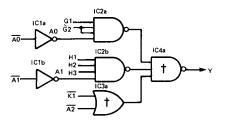

Figure 3.1 shows the logic symbol for a 3-input NAND gate, where A, B and C are the inputs, and Q is the output. An 'AND' function gives A.B.C, but a 'NAND' function modifies this to  $\overline{A.B.C.}$

| Truth table |   |   |   |  |  |  |

|-------------|---|---|---|--|--|--|

| А           | В | С | Q |  |  |  |

| 0           | 0 | 0 | 1 |  |  |  |

| 0           | 0 | 1 | 1 |  |  |  |

| 0           | 1 | 0 | 1 |  |  |  |

| 0           | 1 | 1 | 1 |  |  |  |

| 1           | ò | 0 | 1 |  |  |  |

| 1           | 0 | 1 | 1 |  |  |  |

| 1           | 1 | 0 | 1 |  |  |  |

| 1           | 1 | 1 | 0 |  |  |  |

Figure 3.1. A 3-input NAND gate and truth table

The output from any logic gate is dependent upon the state of all its inputs. In order to fully specify all possible output states it is therefore necessary to consider all possible input states. The usual way to do this is to prepare a *truth table* for the gate. This is also given in the figure. The truth table comprises a column for every input and output. Although it does not matter in what order the various input permutations are considered, it is a good idea to enter these in the form of an ascending binary count. The binary system has a base of 2, and comprises only the digits 0 and 1, therefore each line of the table in question shows the binary equivalent of the decimal numbers 0 to 7.\* In this way it is possible to ensure that no input combination is either missed out or duplicated. The truth table shows that the Q output is always at logic 1 *unless* all of the inputs are at logic 1; when all the inputs are at logic 1 the output is at logic 0.

This description of the NAND gate summarises its action more concisely than the lengthy truth table, and the essence of 'thinking like a designer' is to simplify gate descriptions in this manner. There is then less to remember, and you more quickly come to instinctively know how a particular logic network functions at a glance.

One method of simplifying gate actions is to introduce what is known as the *don't care* condition into truth tables. This technique uses the cross symbol 'X' to indicate 'don't care' conditions: this implies that the output is unaffected by the logic state of any don't care terms. Figure 3.2 is an alternative truth table for the 3-input NAND gate previously considered. It may be seen that the truth table has now been condensed to four lines from eight lines in the original. It is not practical to produce a truth table for every possible input condition for a logic network if there are a great many inputs, and in such cases the don't care symbol is invaluable as a method of simplifying the truth table.

| Truth table |   |   |     |  |  |  |

|-------------|---|---|-----|--|--|--|

| Α           | B | С | · a |  |  |  |

| 1           | 1 | 1 | 0   |  |  |  |

| х           | х | 0 | 1   |  |  |  |

| ×           | 0 | х | 1   |  |  |  |

| 0           | х | X | 1   |  |  |  |

Figure 3.2. Truth table for 3-input NAND gate using 'don't cares'

The idea of utilising an increasing binary count must be discarded in truth tables utilising don't cares, but a sensible pattern should be maintained. A good method is to start with the *unique condition* of the gate which produces a particular output for only one input condition. In the example given in Figure 3.2 this is the condition where all *true* inputs (logic 1) give a *false* output (logic 0). We know that any change to any input affects the output, therefore any input at logic 0 produces a logic 1 at the output. This can be shown in the truth table by considering each input at logic 0 and entering all the

\* Binary arithmetic is considered in more detail in Chapter 8.

other inputs as don't cares - they can be at logic 0 or at logic 1 without affecting the output.

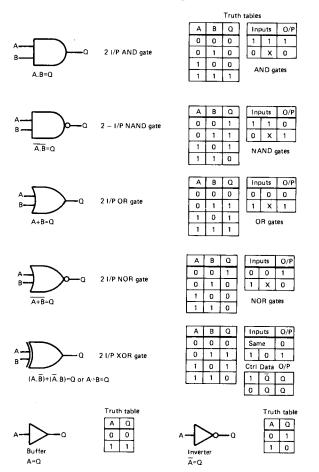

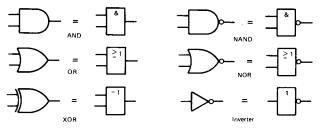

Any logic gate can be described fully by two statements which refer to the two possible output states, and this is what a prospective designer would do well to remember. It is not possible to remember full truth tables, and it is impossible to get a true 'feel' for a circuit if you have to constantly refer to a truth table. In discussing the various logic gates, this method of remembering a gate's function will be emphasised as well as describing it in the more traditional fashion. Figure 3.3 depicts the most common gates. For simplicity, it is usual to consider only 2-input gates.

Figure 3.3. A selection of logic gates and their truth tables

The upper section of the figure shows the logic symbol for a 2-input AND gate. The expression: A.B = Q describes the function of the gate in algebraic form. This is known as Boolean algebra, and utilises the following symbols:

. represents AND

+ represents OR

= may be read as 'gives'.

Thus 'A B = Q' may be read as: 'A AND B GIVES Q'.

The unique condition for this gate is when both inputs are true, giving the output true. The larger of the two truth tables given for the gate is the normal way of representing all logic conditions. This is all very well for a 2-input gate, but a 4-input gate would require 16 lines to fully represent it in this manner. The smaller of the two truth tables introduces don't cares, and this principle is applicable for *all* AND gates, no matter how many inputs. The *inputs* side of this truth table shows in the first line that the unique condition of *all* inputs at logic 1 produces a logic 1 at the output. The second line indicates that if *any* input is at logic 0, the output is at logic 0, irrespective of the state of any other inputs, as indicated by the don't care symbol.

The simple way to remember AND gate action is to think of it as follows:

#### AND GATE: ALL INPUTS AT 1 GIVES OUTPUT AT 1 ANY INPUT AT 0 GIVES OUTPUT AT 0.

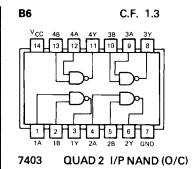

The NAND gate is like an AND gate followed by an inversion. The small circle on the output side of the symbol is the method used to indicate an inversion. The truth table for the NAND gate is identical to that for the AND gate except that the output is inverted (or *complemented*), as shown in the larger truth table for the gate. The Boolean expression  $\overline{A.B} = Q$  should be read as: 'NOT (A AND B) GIVES Q'. The simplified truth table has the same input condition for the unique case, but this time the output is at logic 0. This time any input at logic 0 produces a logic 1 at the output. This gate should be remembered as follows:

#### NAND GATE: ALL INPUTS AT 1 GIVES OUTPUT AT 0 ANY INPUT AT 0 GIVES OUTPUT AT 1.

The OR gate has a different distinctive symbol, and is described by the Boolean expression: A + B = Q, read as: 'A OR B GIVES Q'. As the larger truth table shows, if any input is at logic 1 then the output is at logic 1. This gives rise to the unique condition of logic 0 at the output when all inputs are at logic 0. Note the simplified don't care truth table representation. This gate should be remembered as follows:

#### OR GATE: ALL INPUTS AT 0 GIVES OUTPUT AT 0 ANY INPUT AT 1 GIVES OUTPUT AT 1.

The NOR gate symbol is identical to the OR gate symbol except for the inverting circle on the output line. Like the NAND gate in relation to the AND gate, the NOR gate truth table is similar to the OR gate truth table; the difference is simply that the output is complemented. The Boolean expression is:  $\overline{A + B} = Q$ , read as: 'NOT (A OR B) GIVES Q'. The unique condition is both inputs at logic 0 producing an output at logic 1. This gate should be remembered as follows:

#### NOR GATE: ALL INPUTS AT 0 GIVES OUTPUT AT 1 ANY INPUT AT 1 GIVES OUTPUT AT 0.

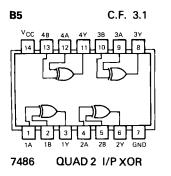

The exclusive-OR gate, abbreviated as 'XOR', is similar to the OR gate, except that it distinguishes the difference between one input at logic 1 and more than one input at logic 1. The distinctive symbol has the double-curved input to signify its 'exclusive' function. Compare the full truth table with that of the OR gate, and it will be seen that the only difference is in the bottom line. With the XOR gate, more than one input at logic 1 produces an output at logic 0. The name can now be appreciated, for the gate detects one input OR another exclusively, as opposed to simultaneously. The simplified truth table has been modified in form to more easily depict this, and relates directly to the easy way of remembering the function of the gate, given below. The Boolean expression: (A, B) +  $(\overline{A}, B) = O$  represents this gate, and may be read as: '(A AND NOT B) OR (NOT A AND B) GIVES Q'. As with ordinary algebra, it is possible to transform this expression into another form which is logically equivalent, but the form given is probably the easiest to understand at this point. The symbol  $\oplus$  can be used to indicate exclusive-OR directly. This gate can most easily be remembered as follows:

ALL INPUTS THE SAME GIVES OUTPUT XOR GATE: AT 0 ONE INPUT AT 1 GIVES OUTPUT AT 1. The XOR gate has a most useful function in logic circuits, in that it may be used to either invert or not invert a *data bit* in accordance with a *control* input. Consider the A input as a control, and the B input as a data input, for example. By studying the full truth table, it may be seen that when A is at logic 0, the Q output is a direct copy of the B input. Thus a control input at logic 0 produces no inversion. When A is at logic 1, however, the Q output is the inverted form of the B input. Thus a control input at logic 1 produces an inversion. This feature is summarised by the lower right truth table for the gate, where the output of 'Q' is obtained from a data input 'Q' when not inverted, or 'Q' when inverted.

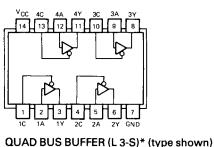

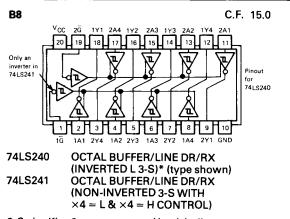

The lower portion of the figure shows simple *buffer* and *inverter* gates. No logical change occurs between the input and output of the buffer gate, hence the Boolean expression A = Q. The gate is useful where it is required to connect more inputs to a particular output than are allowed as direct connections. If a particular gate is limited to a fanout (i.e. loading) of 10 gates, then if a buffer gate forms one of the loads, 9 inputs can be connected directly to the output in question, and a further 10 to the buffer gate, without any logical modification.

The inverter gate has a similar symbol, but with the addition of the now expected inverting circle on the output. This gate complements the logic state applied to the input, hence the Boolean expression:  $\overline{A} = Q$ . Thus a logic 0 in produces a logic 1 out, and a logic 1 in produces a logic 0 out.

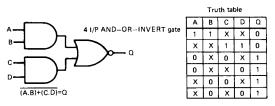

Figure 3.4. A 4-input AND-OR-INVERT gate and truth table

Another logic function which can be quite useful is performed by what is known as an AND-OR-INVERT gate. This is shown with its truth table in Figure 3.4.  $(A \cdot B) + (C \cdot D) = Q$  is the Boolean expression read as: NOT ((A AND B) OR (C AND D)) GIVES Q. Because there are four inputs, a full truth table would require 16 lines. For this reason only the simplified truth table is given. This shows that the unique condition of logic 0 out results from either (or both) of A AND B OR C AND D being at logic 1. If any input is low in both input pairs then the output is at logic 1. Remember this gate as follows:

AND-OR-INVERT GATE: EITHER INPUT PAIR AT 1 GIVES OUTPUT AT 0 ALL INPUT PAIRS WITH A 0 GIVES OUTPUT AT 1.

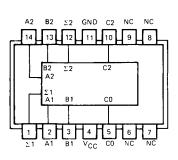

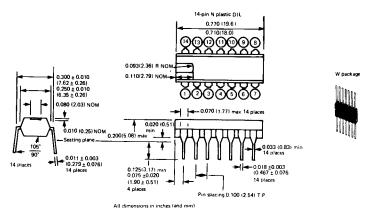

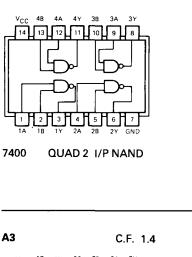

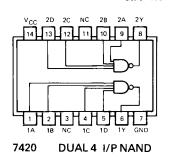

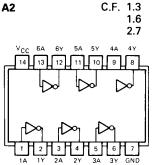

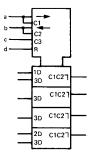

Appendices at the rear of this book give a selection of the most useful digital devices in the SN7400 series, where several of the above gate types can be obtained on a single integrated circuit. The smallest of these dual-in-line encapsulations has 14 pins, as illustrated in Figure 3.5. Two of these pins are required for the power

Figure 3.5. The 14-pin dual-in-line plastic encapsulation

supplies, leaving 12 functional pins. This conveniently allows for four identical 2-input logic gates.

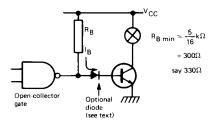

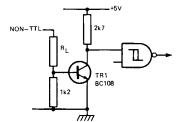

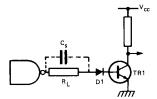

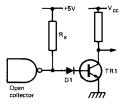

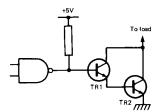

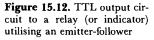

Many of the more popular logic gates are also available with open-collector outputs instead of the push-pull or *totem-pole* arrangement shown in Figure 2.4; with reference to this figure, such devices do not include R4, TR3 and D2. The logic 0 output condition is therefore unchanged, but the logic 1 condition simply presents a high impedance output, and an external connection must employ a pull-up resistor to +5V. Such gates can be useful for driving loads,

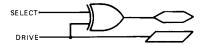

Figure 3.6. Examples of 3-state gates: (a) enabled with control high; (b) enabled with control low

or several such gates can be linked to a common pull-up resistor to give what is termed a wired-OR connection.

Another form of output available with certain devices is known as *three-state\**. As the name suggests, such devices present three alternative forms of output: logic 1, logic 0, and also a high impedance state. The high impedance state or the logic states are output in accordance with a control line C, as shown in Figure 3.6. The high impedance state allows any number of these gates to be

<sup>\*</sup> The name 'tri-state' is also used, but this is a manufacturer's trade mark.

commoned in order to route different data lines to a common destination or destinations. A number of associated data lines connected in this manner are known as a *data highway*; thus data highways link multiple data sources to one or more destinations.

The examples given in the figure show the two options available; in Figure 3.6(a) the control input must be high to enable the gate, and in Figure 3.6(b) the control input must be low to enable the gate. When the gates are not enabled they present a high impedance output. The control circuitry must ensure that only one gate is enabled at once in each group of gates with commoned outputs.

It may therefore be seen that there is a wide variety of devices for the designer to choose from, and invariably a particular type will suit his needs.

Different packages are available for different applications, such as the ceramic encapsulation for military environments. Most commercial systems employ the cheaper plastic dual-in-line (DIL) encapsulations, as illustrated. More complex devices utilise similar packages with more pins. In all cases, however, pinning is always from pin l at the top left-hand side of the device, when viewed from the top with the identification mark farthest away from you. This is generally a notch or central mark, as shown, but replaced sometimes by a dot next to the number l pin. The pins are then numbered *down* the left-hand side and back up the right-hand side, as shown in Appendix A.

There is a preferred standard for the power supplies, which places ground as the bottom left-hand pin, and  $V_{cc}$  as the top right-hand pin, but there are numerous exceptions to this, and this should never be taken for granted.

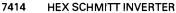

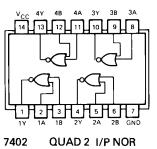

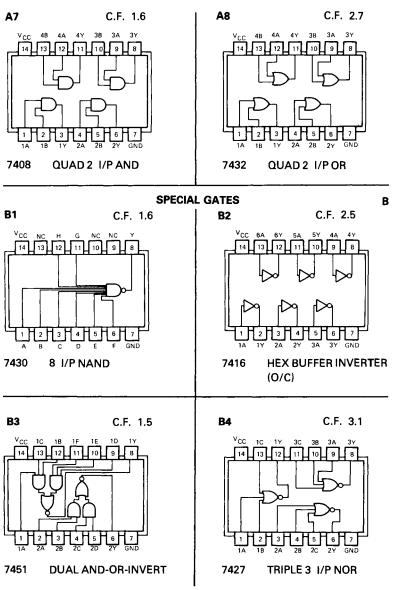

Commercial devices containing logic gates discussed in this chapter are included in Appendix A as follows.

| Gate                | Number in package | Type number | Appendix ref. |

|---------------------|-------------------|-------------|---------------|

| 2 i/p AND           | 4                 | 7408        | A7            |

| 2 i/p NAND          | 4                 | 7400        | Al            |

| 2 i/p OR            | 4                 | 7432        | A8            |

| 2 i/p NOR           | 4                 | 7402        | A6            |

| 2 i/p XOR           | 4                 | 7486        | B5            |

| Buffer              | 6 (with open-col) | 7417        | A2 (note)     |

| Inverter            | 6                 | 7404        | A2            |

| 4 i/p AND-OR-INVERT | 2                 | 7451        | <b>B</b> 3    |

| 3-state buffers     | 4                 | 74125/6     | <b>B</b> 7    |

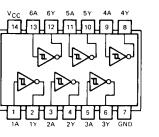

| Schmitt inverter    | 6                 | 7414        | A4            |

#### Schmitt triggers

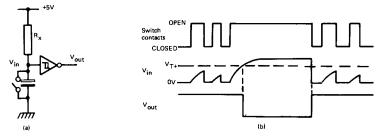

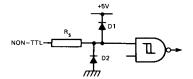

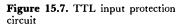

The previous chapter described the internal structure of a typical TTL gate, and emphasised that all inputs and outputs switch between high and low states. Certain gates may contain quite a number of stages, and if an input is held at some intermediate voltage level the internal circuit may not switch to one of the two logic states: this could lead to transient conditions and internal oscillations. For this reason it is important that switching times are always very fast. These should typically be of the order of 10ns  $(10^{-8} s)$ .

This may sound an enormous problem to the person more familiar with linear circuits of a slower variety, but it should be remembered that logic gates naturally achieve the switching time requirements, and the only problem comes where it is necessary to interface a logic circuit with a slower section of discrete circuitry, as with a transistor input, for example. This is where the Schmitt trigger comes in. The linear designer will be familiar with discrete versions of the Schmitt trigger, but in logic terms, it is simply another gate, as shown from the last entry in the table of gate types given above.

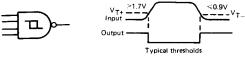

Slow inputs should not be connected to ordinary logic gate inputs, except under special conditions, which will be discussed in Part 2. Slow inputs may be connected to Schmitt triggers, since these provide fast output switching between logic states once the input has crossed upper or lower threshold voltages. Figure 3.7 shows the symbol for a 4-input Schmitt trigger arranged as a NAND gate (7413 is a dual 4-input version). The waveform diagram shows how the output changes in relation to an input, assuming that the other inputs are at logic 1. The typical positive-going threshold voltage ( $V_{T+}$ ) is 1.7V and the negative-going threshold ( $V_{T-}$ ) is typically 0.9V. The hysteresis between these two figures prevents oscillation at an intermediate voltage level.

Figure 3.7. A 4-input Schmitt trigger (NAND) gate

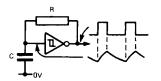

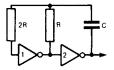

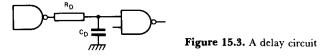

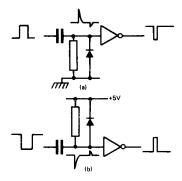

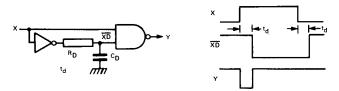

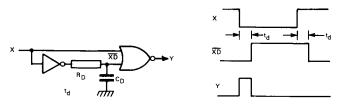

Schmitt triggers are available as 4 or 2-input NAND gates, or as simple inverters (as listed in the preceding table). The hysteresis symbol within an ordinary gate outline distinguishes it as having Schmitt inputs. Because these gates will accept slow edges, they can be used after small CR type delays.

#### Logic networks

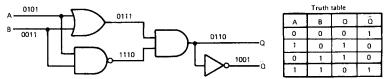

Figure 3.8 depicts a very simple logic network: a combination of logic gates connected together to form a logic circuit. If it is required to determine the output conditions for all input conditions, then one method of achieving this is to prepare a truth table. In the figure this has been done by considering every possible input condition. The 1's and 0's written above the lines indicate the *sequence* that these conditions have been considered in. Thus A = 0 and B = 0 is the first condition considered, which produces logic 0 at the OR gate output, logic 1 at the NAND gate output, logic 0 at the AND gate output, and logic 1 at the inverter output. This is a useful circuit to study since it contains most of the gate types. Satisfy yourself of the validity of the truth table by considering all the conditions.

Once this has been done, it is interesting to note that the circuit without the inverter is the equivalent of the exclusive OR gate. Compare the truth table with that shown in Figure 3.3. Here is a simple method of obtaining an XOR function without using an XOR gate.

Figure 3.8. Considering all possible states for a logic network

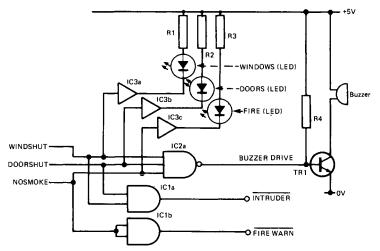

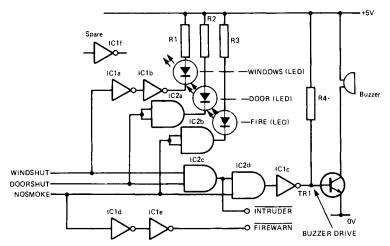

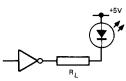

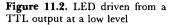

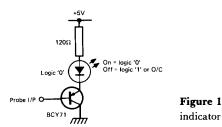

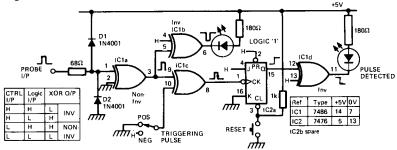

So far we have only considered logic gates in terms of meaningless A, B, C and Q terms. It is perhaps a little more inspiring at this stage to consider a simple logic circuit which has a practical application. In this way it may be better appreciated how useful logic can be. Figure 3.9 shows some indicator logic for a combined burglar and fire alarm system. It drives an alarm buzzer if a window is opened, a door is opened, or if smoke is detected. A light emitting diode (LED) indicates the nature of the alarm, and two outputs are provided to drive other equipment in order to give alarms to the police station for an intruder, or the fire station for a fire.

Logic lines are best labelled with a mnemonic which suggests their function. Thus the inputs are labelled WINDSHUT to indicate that all windows are shut, DOORSHUT to indicate that all doors are shut, and NOSMOKE to indicate that a smoke detector has not detected any smoke. IC3 provides three open-collector buffer gates (App. A2 note) for driving the LEDs; these are non-inverting gates. If any of the inputs goes false\*, i.e. to logic 0,

<sup>\*</sup> Positive logic is used throughout this book.

Figure 3.9. A practical application of logic gates

the output of the appropriate buffer gate also goes low, thereby drawing current through the LED-resistor combination to indicate the nature of the alarm.

All inputs at logic 1 provide a logic 0 output at IC2a NAND gate, which holds off TR1, but if one or more of the inputs goes false, the output goes high, allowing current to flow through R4 into the base of TR1, so switching on the alarm buzzer. R4 provides for a higher base current than the NAND gate could provide in its high state. If WINDSHUT or DOORSHUT goes false, the output of ICla AND gate also goes false, making the **INTRUDER** output go active; the bar indicates that this output line is active low. If NOSMOKE goes false then **FIREWARN** goes active low. IClb is simply used to provide a buffer between the output line and the NOSMOKE input line, but it has no logical significance because the gate is noninverting. The two inputs of this gate are tied together purely for convenience: all unused gate inputs should be taken to a logic level, and an alternative would be to tie one input to logic 1. As explained in the previous chapter, when inputs to a single gate are tied together as shown, they only form a single gate load to a low-driving input.

The integrated circuits used in this circuit are included in Appendix A as follows:

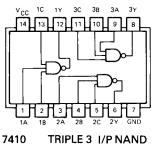

IC1 – 7408 – quad 2 i/p positive AND gates (App. A7).

IC2 – 7410 – triple 3 i/p positive NAND gate (App. A3).

IC3 - 7417 - hex buffers/drivers with open collector high voltage outputs (App. A2).

4

### **Optimisation versus minimisation**

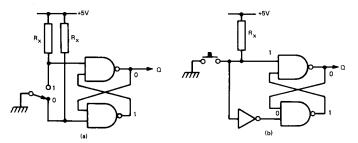

The previous chapter showed how *Boolean algebra* lends itself to expressing logic circuits in mathematical terms. Like ordinary algebra, by following certain rules it is possible to manipulate the terms and obtain equivalent but different expressions; it is also possible to simplify logical expressions. Another method employed to simplify logical conditions is to draw what are termed *Karnaugh maps*; these allow all possible logical permutations to be displayed in graphical terms.

Both the above methods lead to what I have termed *minimisation* of a logical requirement, in that they produce the simplest *logical* solution. These techniques are extensively documented in other literature, and are the subject matter of the more traditional digital courses, therefore this chapter will only describe them in sufficient detail to show their usefulness – and limitations. Whilst such techniques lead to minimisation, this is not the same thing as *optimisation* of a logic circuit, in practical terms; this chapter aims to show the difference.

#### **Boolean algebra**

George Boole devised an algebraic method of converting logical statements into mathematical terms; it was intended as a tool for the logician. It was Shannon who recognised its use when analysing circuit conditions as long ago as 1938. He used it to analyse mechanical switching, but today it is the perfect mathematical method of expressing logic circuits. We shall now look briefly at the rules of Boolean algebra, for it will be appreciated that by simplifying a Boolean expression we can simplify the associated logic network.

Below are given the basic laws of Boolean algebra. Many see these purely in mathematical terms, but the reader is encouraged to visualise them in terms of their gate equivalents. In this way their significance – and truth – will be better understood.

#### Laws of Boolean algebra

| Gating                              | AND 0.0 = 0 0.1 = 0 1.1 = 1 A.0 = 0 A.1 = A                         | 0 + 0 = 0 = 0<br>0 + 1 = 0<br>1 + 1 = 0<br>A + 0 | = l<br>= A                         | $\overline{0} = 1$ |

|-------------------------------------|---------------------------------------------------------------------|--------------------------------------------------|------------------------------------|--------------------|

| Identity                            | $A \cdot A = A$ $A(A + B) = A$ $A(A + B) = A$                       | A<br>A.B                                         | $A + A$ $A + A$ $A + \overline{A}$ | B = A              |

| Double negative                     | $\overline{\overline{\mathbf{A}}} = \mathbf{A}$                     |                                                  |                                    |                    |

| Commutative laws                    | $A \cdot B = B \cdot A$                                             |                                                  | A + B                              | = B + A            |

| Associative laws                    | $A + (B + C)$ $A \cdot (B \cdot C) = ($                             |                                                  |                                    | C                  |

| Distributive laws                   | A.(B + C) = (A.B) + (A.C)<br>A + (B.C) = (A + B).(A + C)            |                                                  |                                    |                    |

| De Morgan's Theorem:<br>First Rule: | negation of lo $\overline{A + B} = \overline{A} \cdot \overline{B}$ | -                                                | ım                                 |                    |

| Second Rule:                        | negation of lo $\overline{A \cdot B} = \overline{A} + \overline{B}$ |                                                  | roduct                             |                    |

Taking just a few examples will show how the above rules may be visualised in terms of their equivalent gates. Once you have learned how the gates behave (and it is essential that you do), the above expressions make immediate sense. By relating the expressions to gate equivalents you obtain a practical grasp instead of learning arbitrary laws in the more usual parrot-fashion.

Firstly consider an AND gate. By definition, this requires all inputs to be at logic 1 for a logic 1 at the output, therefore the first three gating AND terms are seen to be true. If we now consider an unknown input represented by A, it is equivalent to a don't care input if the other input is at 0, therefore the output is also 0. If the A input is combined with a 1 input, however, the output will be the same as the A input, hence  $A \cdot I = A$ . If in doubt, study the truth

table given in Figure 3.3. Having satisfied yourself of this much, carry out a similar exercise with the OR gate terms.

Since there are only two logical states, 0 and 1, then clearly  $\overline{1}$  must be equivalent to 0, or conversely,  $\overline{0}$  equivalent to 1. The complementary expressions are also self-evident. If A and  $\overline{A}$  are inputs to an AND gate, they must always differ, therefore the unique condition of all 1's producing an output of 1 can never be achieved, the output always being 0. If A and  $\overline{A}$  are applied to an OR gate, one of them must always be at 1, therefore the output is always at 1.

The Identity laws are simpler than they look, if you think about them. For example, if the terms A and A. B are applied to the inputs of an OR gate, the output will be at 1 any time A is true; since A is required in both terms, the output is equivalent to A; if A is false, the output will be at 0. The double negative is obvious, for if something is NOT (NOT A), it must be A. The Commutative laws show that there is no significance in order – apples and pears are the same as pears and apples. The Associative laws remind us of ordinary algebra, as do the Distributive laws, where we are factorising. Draw logic circuits to represent any expressions you are in doubt about and all should become clear (see Figure 3.8 for the technique).

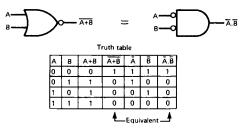

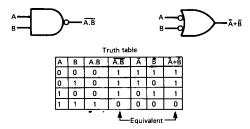

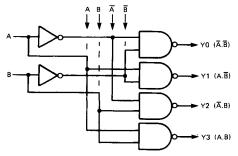

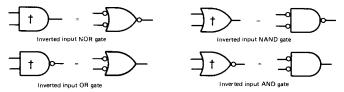

Figure 4.1. Interpreting De Morgan's First Rule using a NOR gate

De Morgan's Theorem is a little more difficult to follow, but both rules can be proven by drawing the truth tables for the indicated gates and then comparing them. Figure 4.1 shows this for De Morgan's First Rule:  $\overline{A + B} = \overline{A}$ .  $\overline{B}$ , using a NOR gate on the left for the left-hand term, and an AND gate with 'notted' inputs on the right, for the right-hand term; in the latter case, the inverting circles on the inputs create  $\overline{A}$  and  $\overline{B}$  from the true A and B inputs. The NOR gate section of the truth table is identical to that seen before in Figure 3.3 (except that an OR column has been added for clarity); the  $\overline{A}$  and  $\overline{B}$  columns are the complements of the A and B columns, and the far right-hand column is an AND of the negated  $\overline{A}$  and  $\overline{B}$ columns which immediately precede it. By comparing the columns representing the outputs of these two gates it can be seen that they are identical, thereby proving the rule. In practical terms it means that a NOR gate can perform an AND function with negated inputs.

De Morgan's Second Rule is similarly proven in Figure 4.2 using a NAND gate for the left-hand term  $(\overline{A}, \overline{B})$ , and an OR gate with inverting inputs for the right-hand term  $(\overline{A} + \overline{B})$ . Once again it may be seen that the outputs from these two gates are identical. In practical terms this indicates that a NAND gate can be used to provide an OR function with inverted inputs.

Figure 4.2. Interpreting De Morgan's Second Rule using a NAND gate

Logic circuits frequently produce inverted signals at a point where non-inverted signals are required to perform a particular function directly. For example, if  $\overline{A}$  and  $\overline{B}$  are directly available and the function A + B is required, the optimum solution is to use a NAND gate, which produces the required result directly; the alternative is to use inverters in series with both  $\overline{A}$  and  $\overline{B}$ , and to follow these with an OR gate. Because NAND and NOR gates provide an inversion, it is possible to use combinations of either of these gates to produce any AND/OR/NAND/NOR function, which can be useful where spare gates are available; clearly either a NAND or a NOR gate can be pressed into service as a simple inverter if required.

#### Karnaugh maps

Consider the following Boolean expression, which represents a logic circuit requirement:

$$\begin{array}{ccc} ABC + A\overline{B}C + AB + \overline{B}\overline{C} = Z \\ \textcircled{1} & \textcircled{2} & \textcircled{3} & \textcircled{4} \end{array}$$

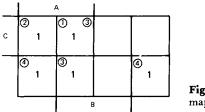

As with ordinary algebra, the absence of a symbol between letters implies '.' (i.e. and AND relationship, in this context). Figure 4.3 is a Karnaugh map for three variables, which in this case are A, B, and C. The first two columns represent A true, the two central columns represent B true, and the upper row represents C true. Thus the top left-hand square represents the logical condition  $\overline{ABC}$ , and the bottom right represents  $\overline{\overline{ABC}}$ .

Figure 4.3. A simple Karnaugh map for three variables

If 'l' is now marked in the various squares to plot the logical expression given above, the entries shown in the figure will be obtained. The circled numbers beneath the terms in the Boolean expression match the related squares marked by similar circled numbers in the Karnaugh map\*. It may be seen that the shorter the term, the more squares it specifies. In this case, the square representing A B C is covered by the first and the third Boolean terms.

The Karnaugh map allows us to see a simplified logical expression. This is derived by grouping together adjacent squares in the map, where it may be visualised that left and right-hand sides bend round and touch, and upper and lower sides do likewise. Thus A describes the four squares in the left-hand block of the map, leaving only one required square not covered. A simplified expression is:  $A + \overline{B} \overline{C}$ .

#### A combined example

Let us suppose that a circuit is required to produce an output Z from the input conditions as described by the following expression:

$$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + AB\overline{C} + ACD = Z$$

$$(1) \qquad (2) \qquad (3) \qquad (4) \qquad (5)$$

By applying the laws of Boolean algebra, this may be simplified as follows:

$$\overline{AC}(\overline{B} + B) + B\overline{C}(\overline{A} + A) + ACD = Z$$

$$\overline{AC} \cdot 1 + B\overline{C} \cdot 1 + ACD = Z$$

$$\overline{AC} + B\overline{C} + ACD = Z$$

$$C(\overline{A} + AD) + B\overline{C} = Z$$

\* The circled numbers are purely a teaching aid.

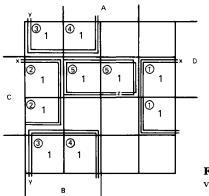

Figure 4.4. A Karnaugh map for four variables

Figure 4.4 shows the same expression plotted on a four variable Karnaugh map in the same manner as before. This then leads to a simplified expression obtained from the borders marked x, y and z on the map, corresponding to the penultimate line in the Boolean simplification (x giving  $\overline{AC}$ ; y giving  $\overline{BC}$ ; z giving  $\overline{ACD}$ ). It can also be seen that the final Boolean expression above is equally true by inspection of the Karnaugh map.

One final word about Karnaugh maps. If more than four variables are involved, an extra dimension is needed to cope, and arrays are needed! Things really tend to get out of hand at this point and the designer should be seeking another more practical approach.

#### Optimisation

Let us now consider whether the techniques of Boolean algebra or Karnaugh maps are the final solution when it comes to effective logic design. It will be appreciated that such procedures lead to *minimisation* of the logic function, but is this the same thing as *optimisation* of components?

The primary objectives of a digital design engineer may be summarised as follows:

- a. Minimum component count.

- b. Maximum availability of components.

- c. Low cost components.

If minimum component count is achieved, we will have won in two ways: firstly on cost, since low component count and low cost go hand-in-hand, and secondly in the reduction of device interconnections. Each and every interconnection is a *potential* source of trouble, therefore the fewer there are, the more inherently reliable the equipment will be. Cost is also reflected in device availability, for maximum availability of component types goes with low cost – the prices of ICs dramatically illustrate the supply and demand equation, with the most popular types being the cheapest, by far. For this reason, the designer should work with preferred types in mind.

The techniques of logic minimisation are obviously useful in reducing a complex logical requirement into its simplest *logical* form, but the designer should then take this as the bare bones of his requirement and optimise his final solution by his manner of implementation. This is best illustrated with a simple example.

Consider the simple alarm/indicator logic circuit discussed at the end of the previous chapter (see Figure 3.9). Ignoring the simple buffer requirements of the LEDs, the logical requirements are as follows:

#### WINDSHUT.DOORSHUT.NOSMOKE = BUZZER DRIVE WINDSHUT.DOORSHUT = INTRUDER NOSMOKE = FIREWARN

The above Boolean expressions describe the circuit requirements, where 'BUZZER DRIVE' is taken to be the input to TR1 base. These three expressions could be used as the basis for three separate Karnaugh maps, but there is little point in drawing these for such simple requirements: the circuit shown in Figure 3.9 can be seen to be the minimum logical solution, for single gates directly implement the above expressions, where:

BUZZER DRIVE is implemented by IC2a

**INTRUDER** is implemented by ICla

FIREWARN is implemented by IClb (providing a required non-inverting buffer).

The original circuit will work using the components listed in Chapter 3, but it can be improved by taking into account the effectiveness with which we are utilising the components. Consider what is used of the original components:

in IC1 only two out of four AND gates are used; in IC2 only one out of three NAND gates is used; in IC3 only three out of six buffer/drivers are used.

Figure 4.5. A cost-effective version of the alarm/indicator logic previously considered in Figure 3.9

It will be seen that this leaves *seven* unused gates, which is clearly an ineffective use of components. Consider the alternative solution given in Figure 4.5.

At first sight the circuit looks needlessly complex, but the advantages are seen when the component count is considered. In this alternative circuit only two ICs are needed:

IC1 – 7404 – hex inverter/drivers (App. A2), containing the only unused gate IC2 – 7408 – quad 2 i/p AND gates (App. A7).

The first economy is to note that the output required for INTRUDER is a partial decode of the BUZZER DRIVE requirement; thus IC2c provides the INTRUDER output directly, but only needs to be NANDed with NOSMOKE to obtain the BUZZER DRIVE requirement. Since IC2c gate has made us use a quad AND gate, IC2d followed by an inverter (AND inverted) is equivalent to the required NAND function. Inverters are invariably required in any logic circuit, therefore hex inverter ICs are extremely cost-effective. In this circuit the inverters are doubled-up in two places to provide non-inverting buffers (double inversion equates to no inversion), i.e. IC1a/IC1b and IC1d/IC1e. The two AND gates IC2a and IC2b provide the remaining non-inverting buffers required to drive the LEDs (NB this circuit would require LEDs having a forward current requirement of less than 16mA).

The percentage effect of *optimisation* techniques such as this grows smaller as the size of a circuit increases – for the more gates of a particular type that are called for, the more gates may be used in a particular device. Part 2 of this book will show how to best approach efficient design from the point of view of component count, but this information should be sufficient to demonstrate that there is a clear distinction between what I have termed *minimisation* and *optimisation*. Optimisation is just as important in a larger circuit, for here the designer is trying to keep down the component count for even more pressing reasons – it could make the difference between needing an extra printed circuit board or perhaps a higher current capability from the power supply, and in these regions the cost difference can be quite considerable.

Thus the need is seen for the designer to appreciate not just the logical significance of his circuits, but the practical aspects as well. It makes no difference whether the enthusiast's pocket or the manufacturer's profitability is being considered, the aim is the same: component optimisation. If you can appreciate the need from the start, it becomes an inner instinct, and an important aid to practical design.

An interesting exercise at this point is to attempt to design a simple circuit optimised for available components. The circuit required in the combined example given earlier is ideally suited to this. Allowing for the fact that the circuit output simplifies to  $C(\overline{A} + AD) + B\overline{C}$ , and that the circuit inputs are A, B, C and D, attempt to design a suitable circuit using only 6 NAND gates<sup>\*</sup>.

\* The few exercises suggested throughout this book should considerably aid the reader's appreciation of the points under discussion. For the book to achieve its objective, they should be attempted.

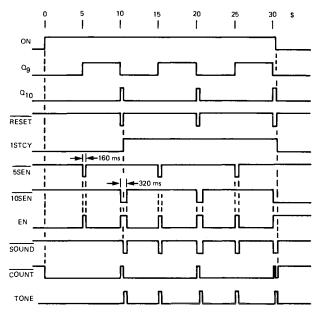

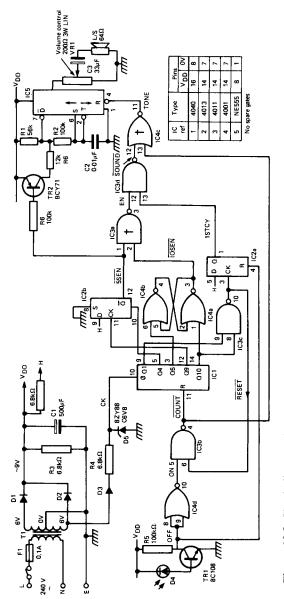

## 5 Timing

The circuits that we have looked at so far have been *static* in nature, i.e. we have only considered them with fixed inputs and outputs. In a practical circuit the sitation is *dynamic* and the inputs and outputs change with time. This may not be an important consideration in simple circuits, but it can become of critical importance in more complex circuits, as will be seen later.

In order to allow us to better understand how a circuit performs with time, the most convenient method of displaying the changing dynamic situation is to draw timing diagrams, sometimes known as waveform diagrams. This chapter introduces the timing diagram in order that it may be used in following chapters. It also demonstrates the importance of timing considerations with reference to hazard conditions.

#### **General considerations**

It will be appreciated by those familiar with linear electronics that there must be a finite delay due to the switching time of a logic gate. Chapter 2 showed the internal structure of a typical TTL gate, and this was seen to comprise several transistors, each of which must switch from one level to another if a change of state is demanded. The time taken for the output of a logic gate to change as a result of an input change is known as the propagation delay, i.e. the time taken for the changed logic condition to 'propagate' through the element. The propagation delay is typically 10 ns for a TTL gate (i.e.  $10^{-8}$ second), however, this is reduced to around 3ns for Schottky TTL, where special diodes prevent internal transistors from saturating. The figure of 10ns should generally be borne in mind for design purposes. If good design practices are followed, the actual propagation of any device should not be significant in any calculations, any more than the actual current gain of a transistor should be a linear design; it is the designer's aim to make variable component parameters irrelevant in the performance of this circuit.

#### **Timing diagrams**

A simple logic circuit will now be considered in an operational context with varying input and output conditions, and it will be shown how these can be illustrated by means of a timing diagram. Figure 5.1 depicts the circuit, and Figure 5.2 the related timing diagram for particular input conditions. For clarity in this example, the input signals are shown above a horizontal chained line, and the resultant outputs are shown below this line.

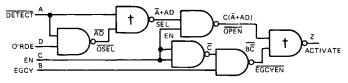

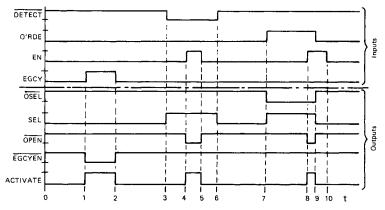

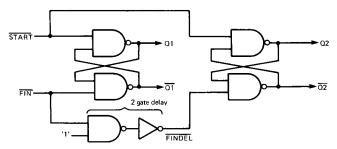

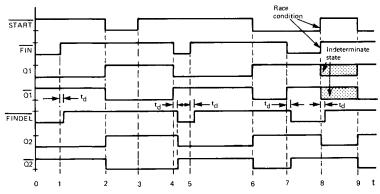

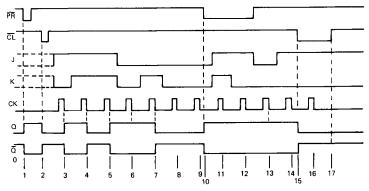

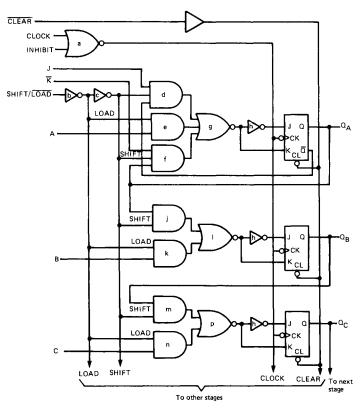

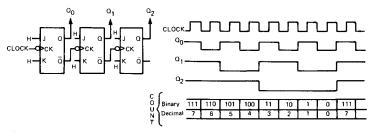

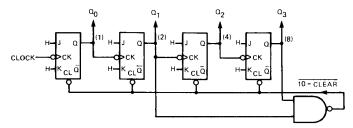

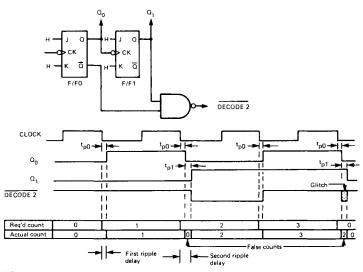

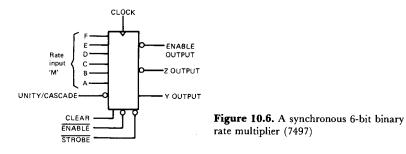

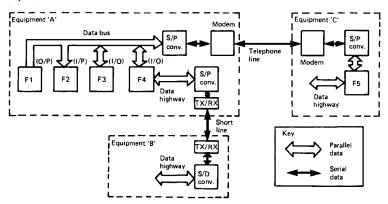

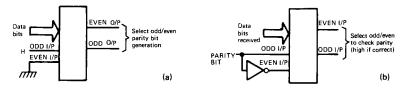

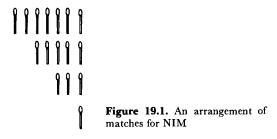

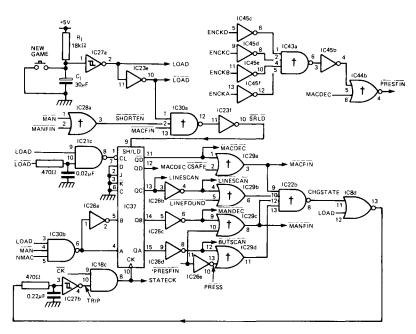

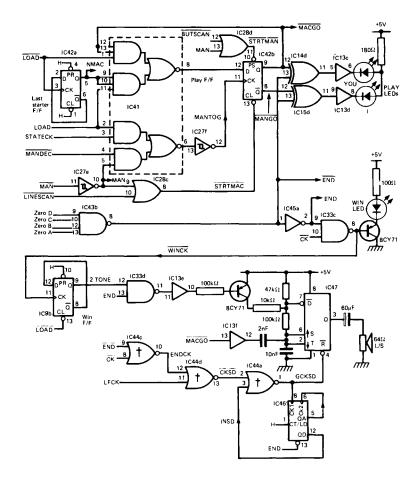

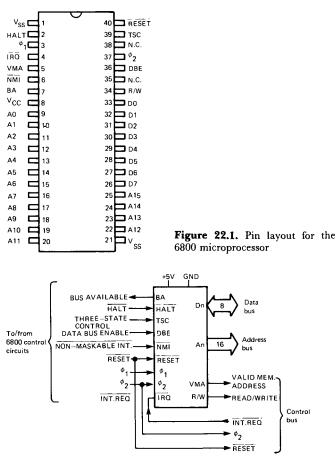

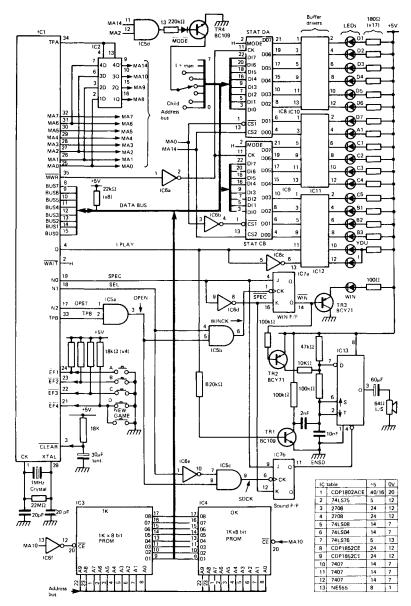

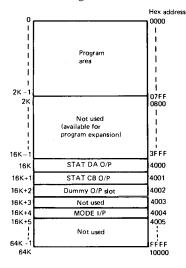

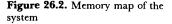

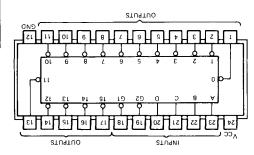

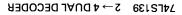

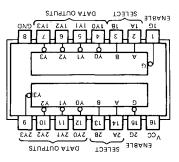

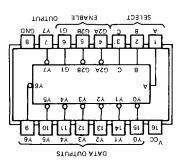

**Figure 5.1.** A circuit producing an output C ( $\overline{A} + AD$ ) +  $\overline{BC}$  (showing added signal names beneath the lines)