Principles of Broadband Switching and Networking

# WILEY SERIES IN TELECOMMUNICATIONS AND SIGNAL PROCESSING

John G. Proakis, Editor Northeastern University

A complete list of the titles in this series appears at the end of this volume.

# Principles of Broadband Switching and Networking

# Tony T. Lee and Soung C. Liew

Copyright © 2010 by John Wiley & Sons, Inc. All rights reserved.

Published by John Wiley & Sons, Inc., Hoboken, New Jersey Published simultaneously in Canada

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978)-750-4470, or on the web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, or online at http://www.wiley.com/go/permissions.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services or technical support, please contact our Customer Care Department within the United States at (800) 762-2974, outside the United States at (317) 572-3993 or fax (317) 572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic books. For more information about Wiley products, visit our web site at www.wiley.com

ISBN: 978-0-471-13901-0

#### Library of Congress Cataloging-in-Publication Data is available.

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

Dedicated to Professor Charles K. Kao for his guidance, and to our wives, Alice and So Kuen, for their unwavering support.

# CONTENTS

| Pr                | Preface                                |                                                       |                                                        |    |  |

|-------------------|----------------------------------------|-------------------------------------------------------|--------------------------------------------------------|----|--|

| About the Authors |                                        |                                                       |                                                        |    |  |

| 1                 | Introduction and Overview              |                                                       |                                                        |    |  |

|                   | 1.1                                    | Switc                                                 | hing and Transmission                                  | 2  |  |

|                   |                                        | 1.1.1                                                 | Roles of Switching and Transmission                    | 2  |  |

|                   |                                        | 1.1.2                                                 | Telephone Network Switching and Transmission Hierarchy | 4  |  |

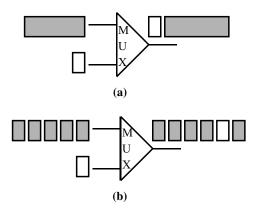

|                   | 1.2                                    | Multiplexing and Concentration                        |                                                        |    |  |

|                   | 1.3 Timescales of Information Transfer |                                                       | scales of Information Transfer                         | 8  |  |

|                   |                                        | 1.3.1                                                 | Sessions and Circuits                                  | 9  |  |

|                   |                                        | 1.3.2                                                 | Messages                                               | 9  |  |

|                   |                                        | 1.3.3                                                 | Packets and Cells                                      | 9  |  |

|                   | 1.4                                    | Broad                                                 | band Integrated Services Network                       | 10 |  |

|                   |                                        | Proble                                                | ems                                                    | 12 |  |

| 2                 | Circuit Switch Design Principles       |                                                       |                                                        | 15 |  |

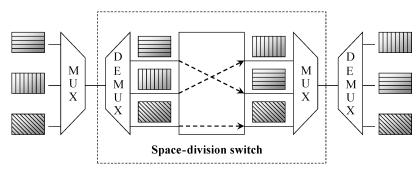

|                   | 2.1                                    | Space-Domain Circuit Switching                        |                                                        | 16 |  |

|                   |                                        | 2.1.1                                                 | Nonblocking Properties                                 | 16 |  |

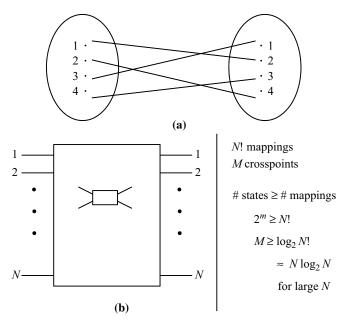

|                   |                                        | 2.1.2                                                 | Complexity of Nonblocking Switches                     | 18 |  |

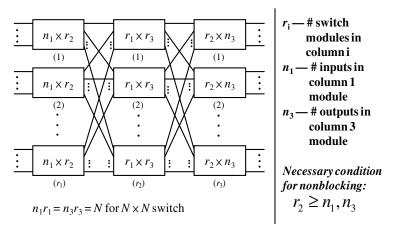

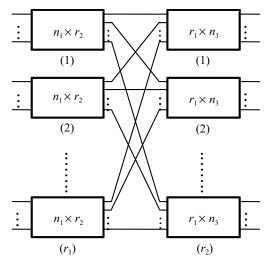

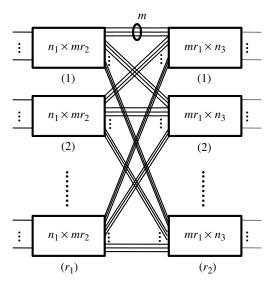

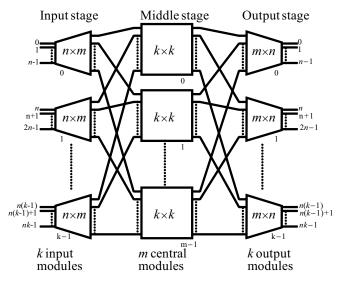

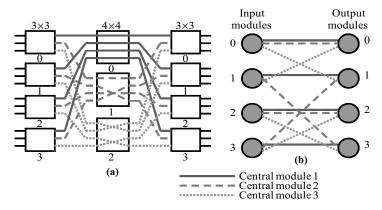

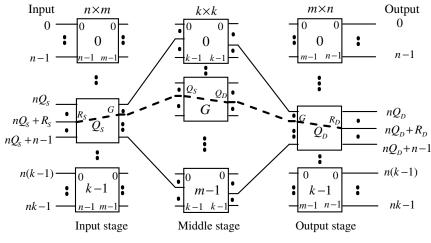

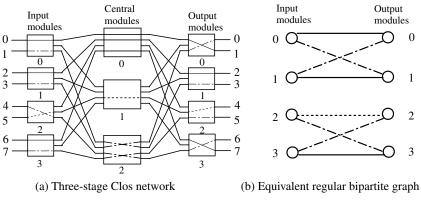

|                   |                                        | 2.1.3                                                 | Clos Switching Network                                 | 20 |  |

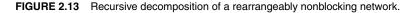

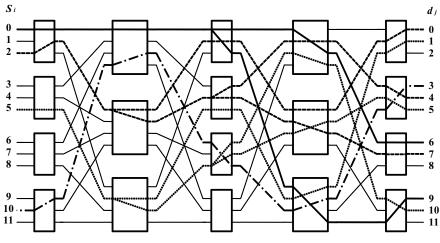

|                   |                                        | 2.1.4                                                 | Benes Switching Network                                | 28 |  |

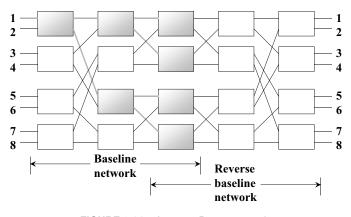

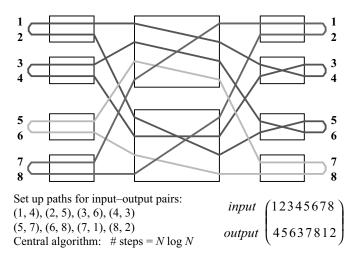

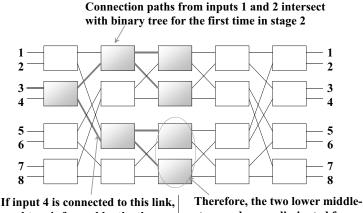

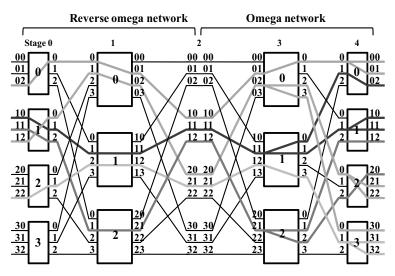

|                   |                                        | 2.1.5                                                 | Baseline and Reverse Baseline Networks                 | 31 |  |

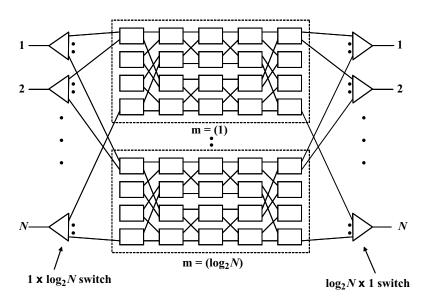

|                   |                                        | 2.1.6                                                 | Cantor Switching Network                               | 32 |  |

|                   | 2.2                                    | 2.2 Time-Domain and Time–Space–Time Circuit Switching |                                                        | 35 |  |

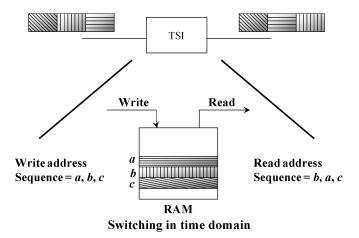

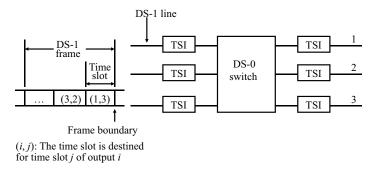

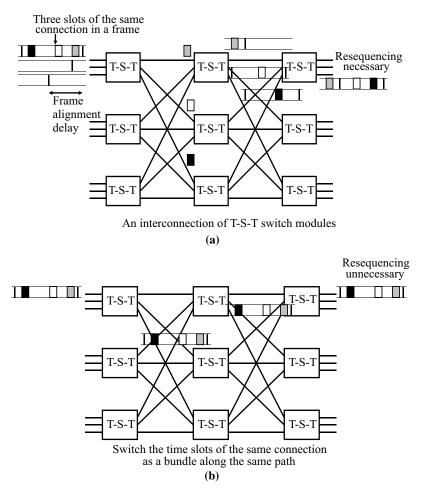

|                   |                                        | 2.2.1                                                 | Time-Domain Switching                                  | 35 |  |

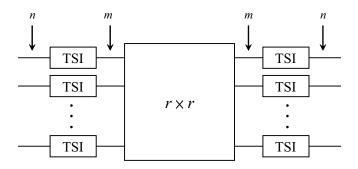

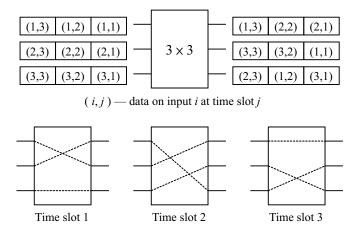

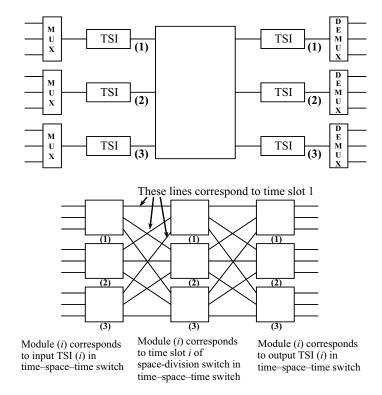

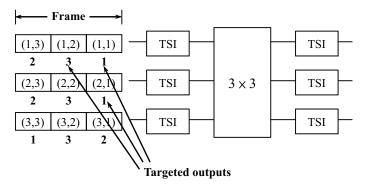

|                   |                                        | 2.2.2                                                 | Time–Space–Time Switching                              | 37 |  |

|                   |                                        | Proble                                                | ems                                                    | 39 |  |

| 3 | Fur                                                    | ndame                             | ntal Principles of Packet Switch Design                    | 43  |  |

|---|--------------------------------------------------------|-----------------------------------|------------------------------------------------------------|-----|--|

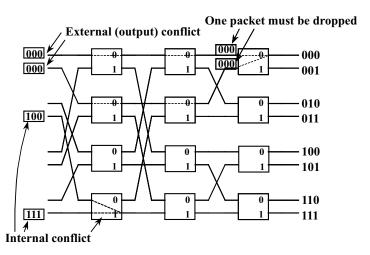

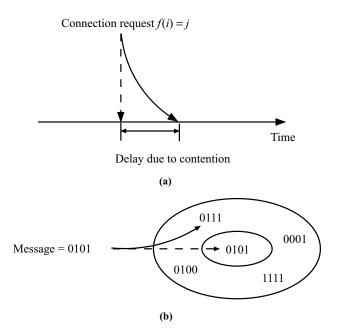

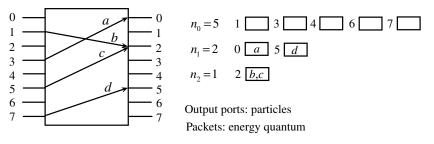

|   | 3.1                                                    | 3.1 Packet Contention in Switches |                                                            |     |  |

|   | 3.2 Fundamental Properties of Interconnection Networks |                                   | mental Properties of Interconnection Networks              | 48  |  |

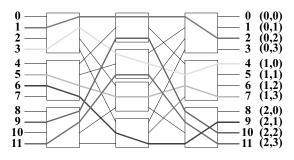

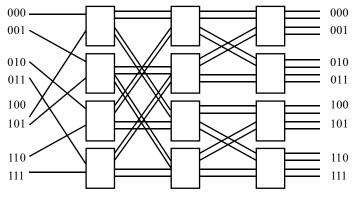

|   |                                                        | 3.2.1                             | Definition of Banyan Networks                              | 49  |  |

|   |                                                        | 3.2.2                             | Simple Switches Based on Banyan Networks                   | 51  |  |

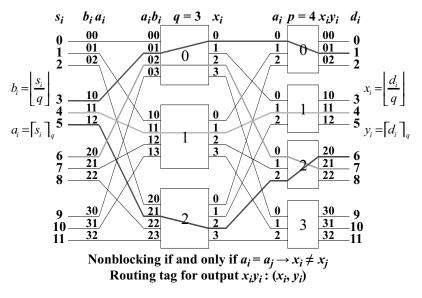

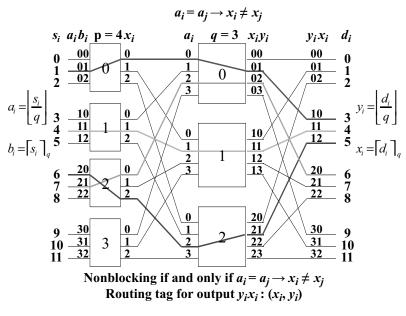

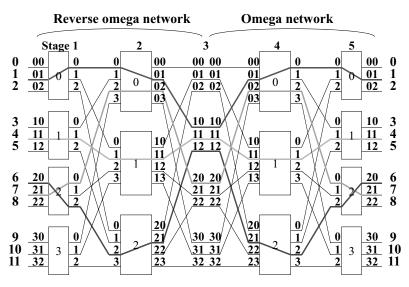

|   |                                                        | 3.2.3                             | Combinatoric Properties of Banyan Networks                 | 54  |  |

|   |                                                        | 3.2.4                             | Nonblocking Conditions for the Banyan Network              | 54  |  |

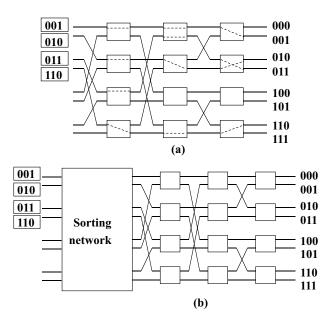

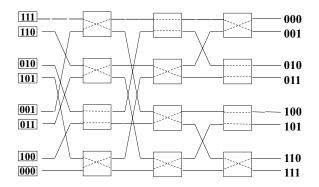

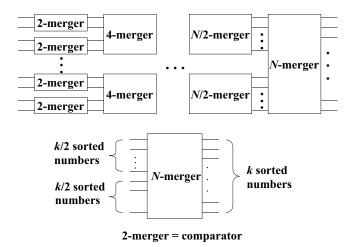

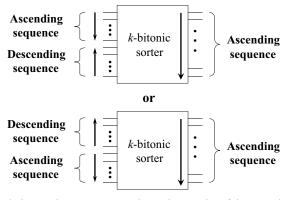

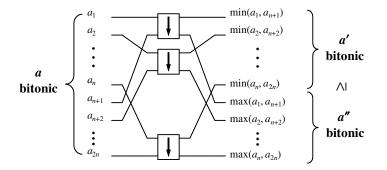

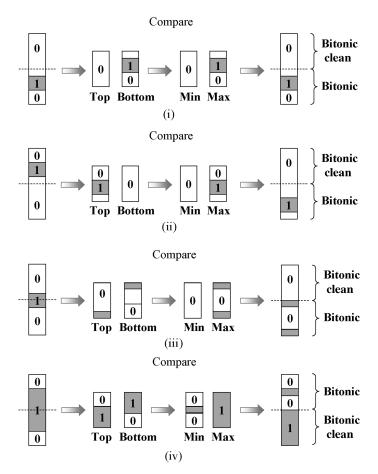

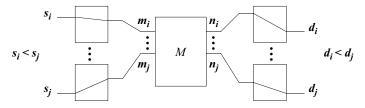

|   | 3.3                                                    | 3.3 Sorting Networks              |                                                            |     |  |

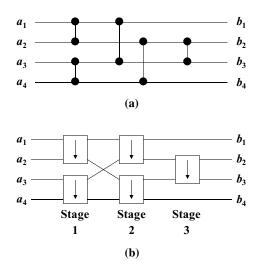

|   |                                                        | 3.3.1                             | Basic Concepts of Comparison Networks                      | 61  |  |

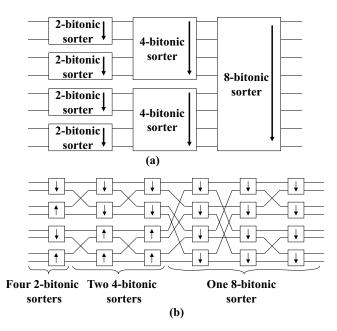

|   |                                                        | 3.3.2                             | Sorting Networks Based on Bitonic Sort                     | 64  |  |

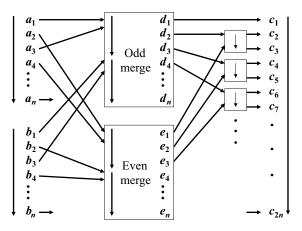

|   |                                                        | 3.3.3                             | The Odd–Even Sorting Network                               | 70  |  |

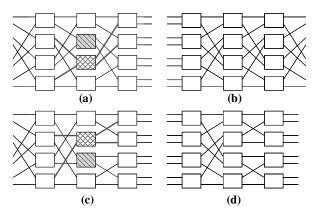

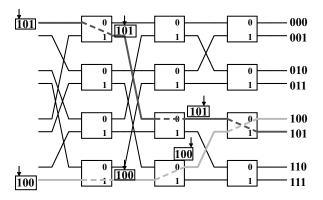

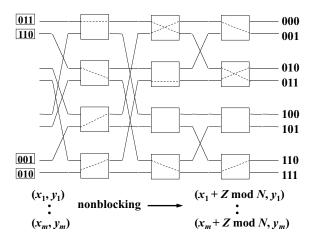

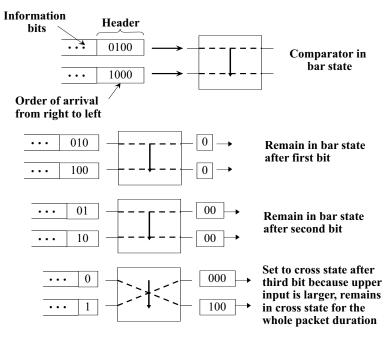

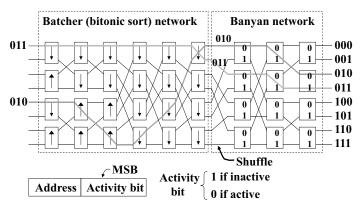

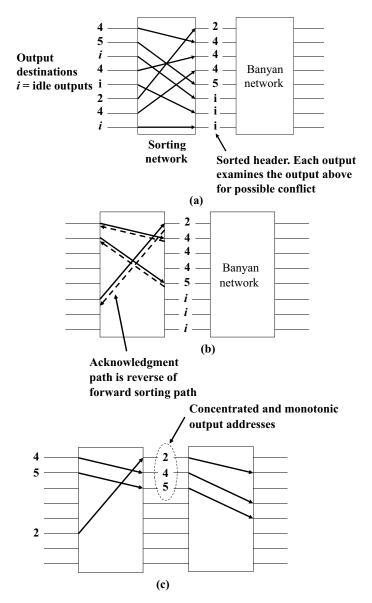

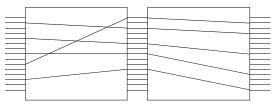

|   |                                                        | 3.3.4                             | Switching and Contention Resolution in Sort-Banyan Network | 71  |  |

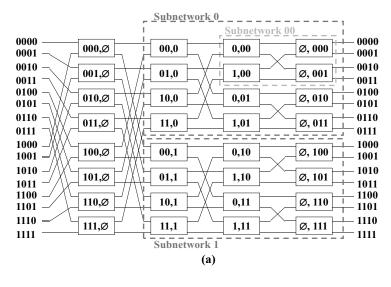

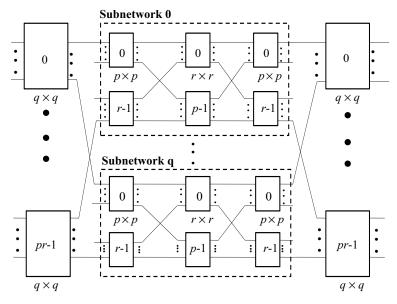

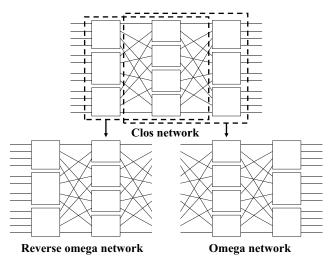

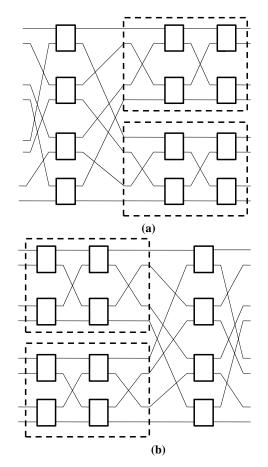

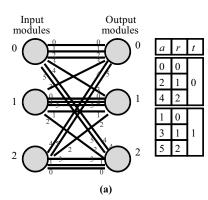

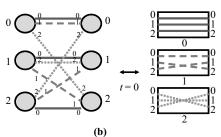

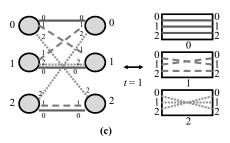

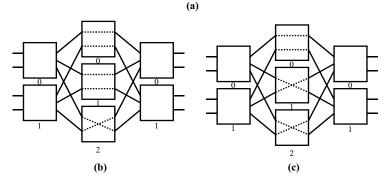

|   | 3.4                                                    | Nonbl                             | locking and Self-Routing Properties of Clos Networks       | 75  |  |

|   |                                                        | 3.4.1                             | Nonblocking Route Assignment                               | 76  |  |

|   |                                                        | 3.4.2                             | Recursiveness Property                                     | 79  |  |

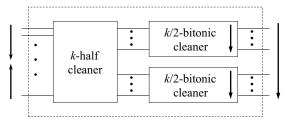

|   |                                                        | 3.4.3                             | Basic Properties of Half-Clos Networks                     | 81  |  |

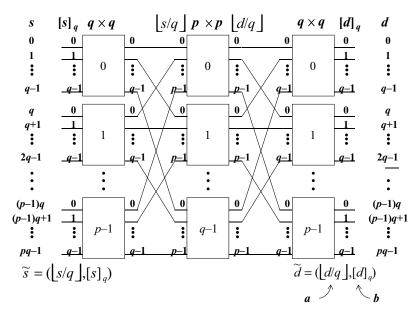

|   |                                                        | 3.4.4                             | Sort-Clos Principle                                        | 89  |  |

|   |                                                        | Proble                            | ems                                                        | 90  |  |

| 4 | Switch Performance Analysis and Design Improvements    |                                   |                                                            |     |  |

|   | 4.1                                                    | Perfor                            | rmance of Simple Switch Designs                            | 95  |  |

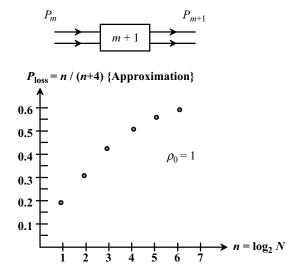

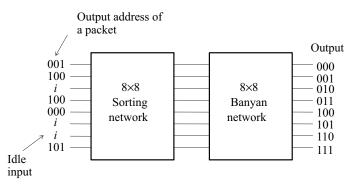

|   |                                                        | 4.1.1                             | Throughput of an Internally Nonblocking Loss System        | 96  |  |

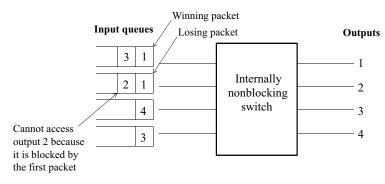

|   |                                                        | 4.1.2                             | Throughput of an Input-Buffered Switch                     | 96  |  |

|   |                                                        | 4.1.3                             | Delay of an Input-Buffered Switch                          | 103 |  |

|   |                                                        | 4.1.4                             | Delay of an Output-Buffered Switch                         | 112 |  |

|   | 4.2                                                    | Desig                             | n Improvements for Input Queueing Switches                 | 113 |  |

|   |                                                        | 4.2.1                             | Look-Ahead Contention Resolution                           | 113 |  |

|   |                                                        | 4.2.2                             | Parallel Iterative Matching                                | 115 |  |

|   | 4.3                                                    | Desig                             | n Improvements Based on Output Capacity Expansion          | 119 |  |

|   |                                                        | 4.3.1                             | Speedup Principle                                          | 119 |  |

|   |                                                        | 4.3.2                             | Channel-Grouping Principle                                 | 121 |  |

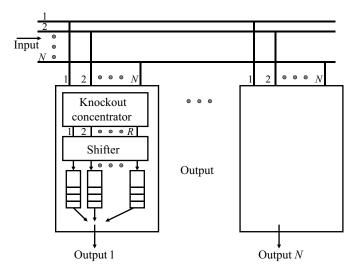

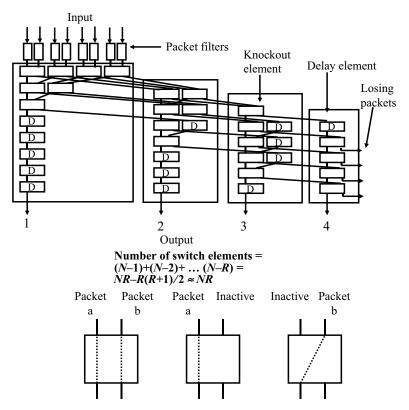

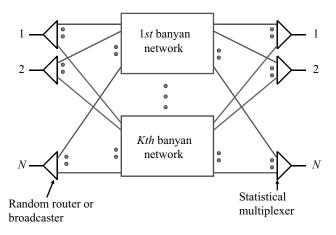

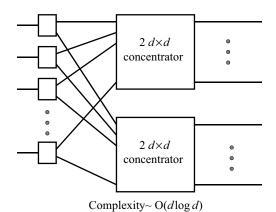

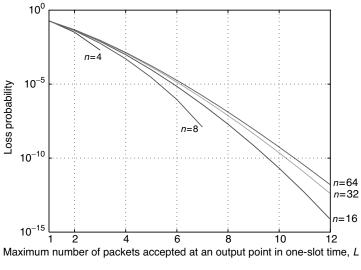

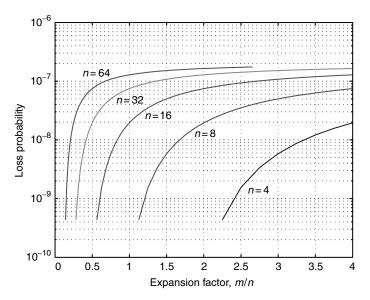

|   |                                                        | 4.3.3                             | Knockout Principle                                         | 131 |  |

|   |                                                        | 4.3.4                             | Replication Principle                                      | 137 |  |

|   |                                                        | 4.3.5                             | Dilation Principle                                         | 138 |  |

|   |                                                        | Proble                            | ems                                                        | 144 |  |

| 5 | Adv                                                    | /ancec                            | Switch Design Principles                                   | 151 |  |

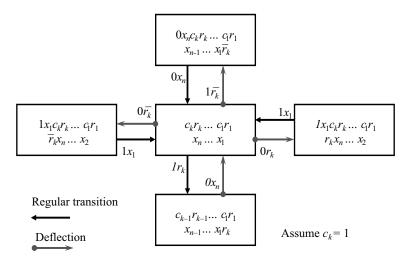

|   | 5.1                                                    | Switch                            | h Design Principles Based on Deflection Routing            | 151 |  |

|   |                                                        |                                   |                                                            |     |  |

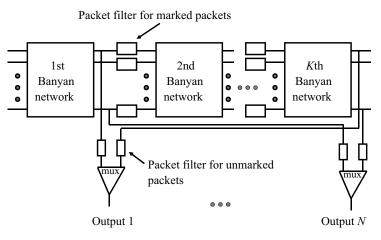

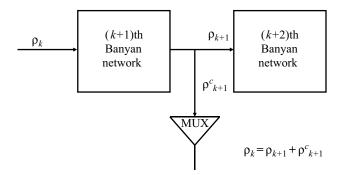

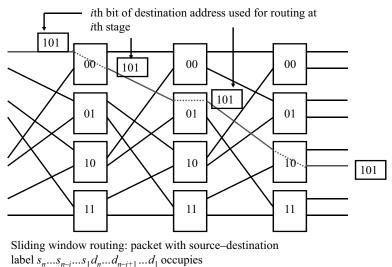

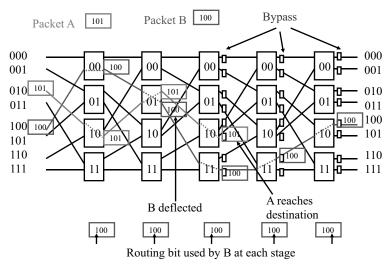

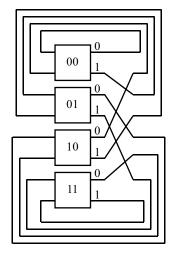

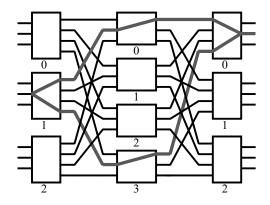

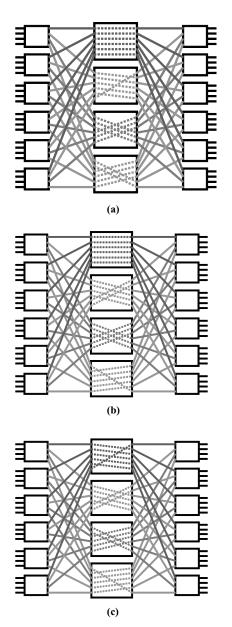

|   |                                                        | 5.1.1                             | Tandem-Banyan Network                                      | 151 |  |

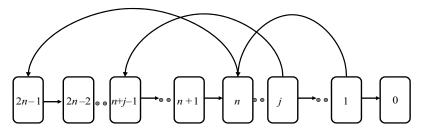

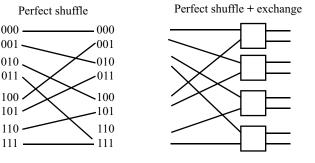

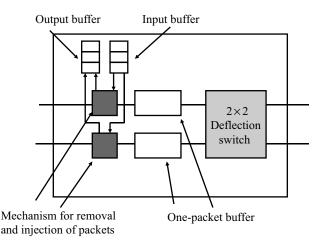

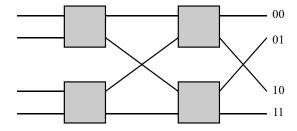

|   |                                                | 5.1.3                                                | Feedback Shuffle-Exchange Network                                     | 158        |  |  |  |

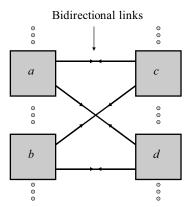

|---|------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------|------------|--|--|--|

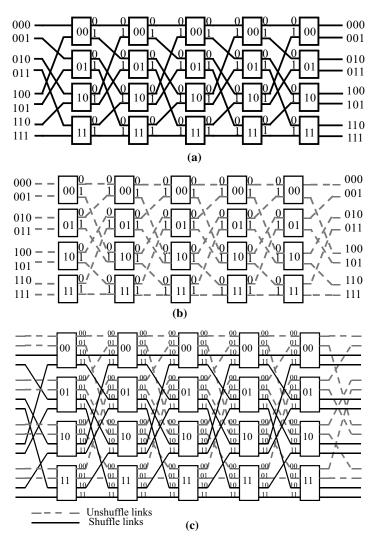

|   |                                                | 5.1.4                                                | Feedback Bidirectional Shuffle-Exchange Network                       | 166        |  |  |  |

|   |                                                | 5.1.5                                                | Dual Shuffle-Exchange Network                                         | 175        |  |  |  |

|   | 5.2                                            | _                                                    |                                                                       |            |  |  |  |

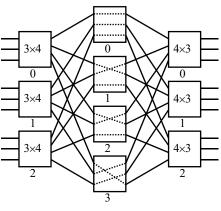

|   | 5.3                                            | Desig                                                | n Principles for Scalable Switches                                    | 187        |  |  |  |

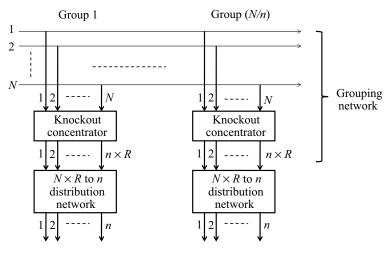

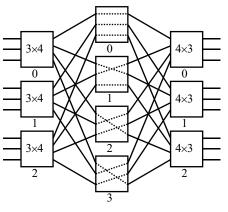

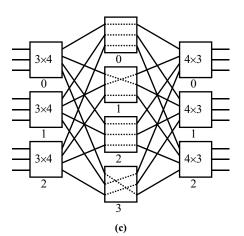

|   |                                                | 5.3.1                                                | Generalized Knockout Principle                                        | 187        |  |  |  |

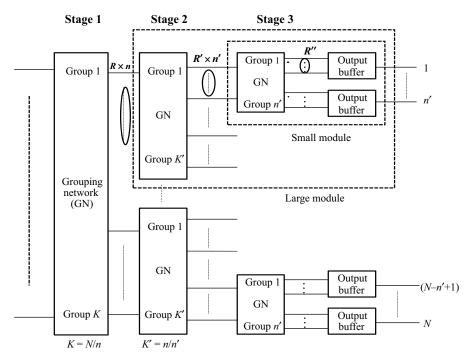

|   |                                                | 5.3.2                                                | Modular Architecture                                                  | 191        |  |  |  |

|   |                                                | Proble                                               | ems                                                                   | 198        |  |  |  |

| 6 | Switching Principles for Multicast, Multirate, |                                                      |                                                                       |            |  |  |  |

|   |                                                | nd Multimedia Services                               |                                                                       |            |  |  |  |

|   | 6.1                                            |                                                      | cast Switching                                                        | 205        |  |  |  |

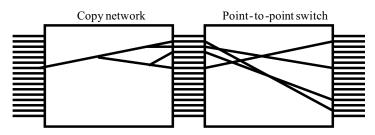

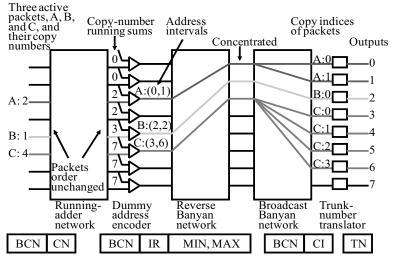

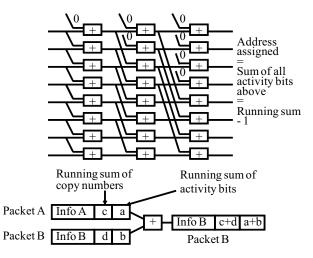

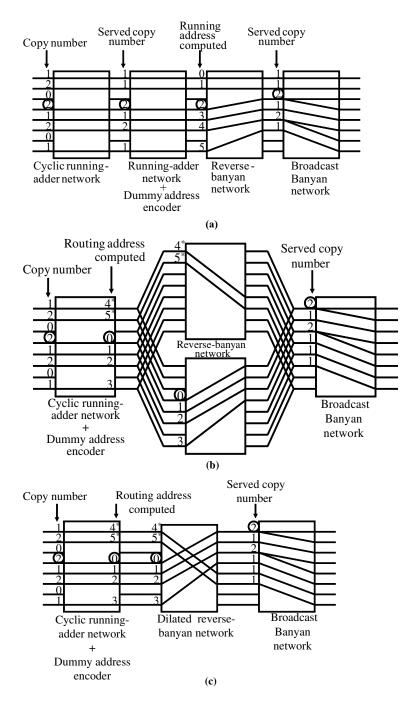

|   |                                                | 6.1.1                                                | Multicasting Based on Nonblocking Copy Networks                       | 208        |  |  |  |

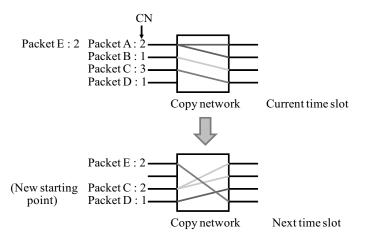

|   |                                                |                                                      | Performance Improvement of Copy Networks                              | 213        |  |  |  |

|   |                                                | 6.1.3                                                | Multicasting Algorithm for Arbitrary Network<br>Topologies            | 220        |  |  |  |

|   |                                                | 6.1.4                                                | Nonblocking Copy Networks Based on Broadcast Clos<br>Networks         | 228        |  |  |  |

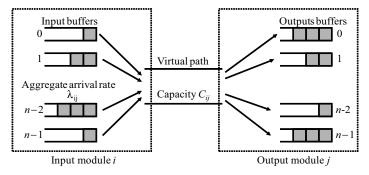

|   | 6.2                                            | Path S                                               | Switching                                                             | 235        |  |  |  |

|   | 0.2                                            | 6.2.1                                                | Basic Concept of Path Switching                                       | 237        |  |  |  |

|   |                                                | 6.2.2                                                |                                                                       | 242        |  |  |  |

|   |                                                | 6.2.3                                                |                                                                       | 249        |  |  |  |

|   |                                                | 6.2.4                                                | Multicasting in Path Switching                                        | 254        |  |  |  |

|   | 6.A                                            | Apper                                                |                                                                       | 268        |  |  |  |

|   |                                                |                                                      | A Formulation of Effective Bandwidth                                  | 268        |  |  |  |

|   |                                                | 6.A.2                                                | Approximations of Effective Bandwidth Based on On–Off<br>Source Model | 269        |  |  |  |

|   |                                                | Proble                                               |                                                                       | 209<br>270 |  |  |  |

| 7 | Bas                                            | ic Cor                                               | ncepts of Broadband Communication Networks                            | 275        |  |  |  |

|   | 7.1                                            |                                                      | ronous Transfer Mode                                                  | 275        |  |  |  |

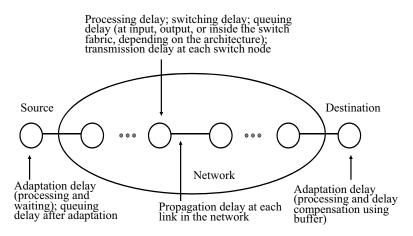

|   | 7.2                                            | Delay                                                | s in ATM Network                                                      | 280        |  |  |  |

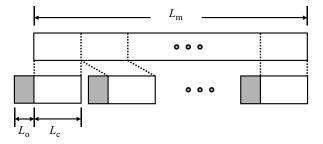

|   | 7.3                                            | Cell Size Consideration                              |                                                                       | 283        |  |  |  |

|   | 7.4                                            | Cell Networking, Virtual Channels, and Virtual Paths |                                                                       | 285        |  |  |  |

|   |                                                | 7.4.1                                                | No Data Link Layer                                                    | 285        |  |  |  |

|   |                                                | 7.4.2                                                | Cell Sequence Preservation                                            | 286        |  |  |  |

|   |                                                | 7.4.3                                                | Virtual-Circuit Hop-by-Hop Routing                                    | 286        |  |  |  |

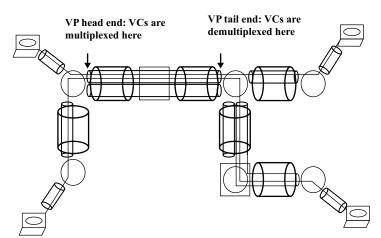

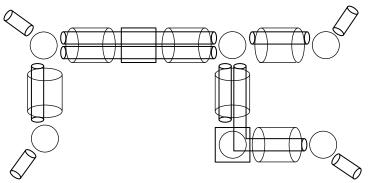

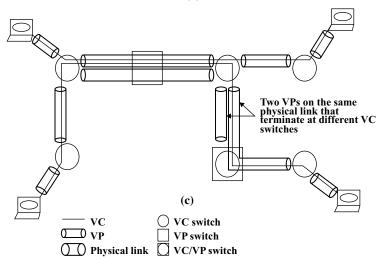

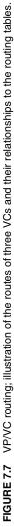

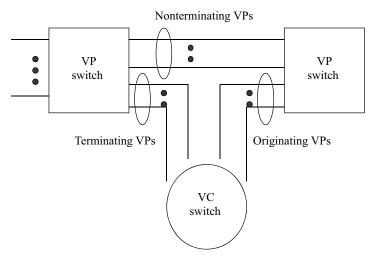

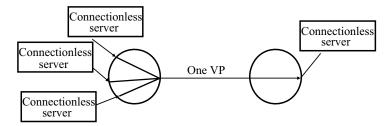

|   |                                                | 7.4.4                                                | Virtual Channels and Virtual Paths                                    | 287        |  |  |  |

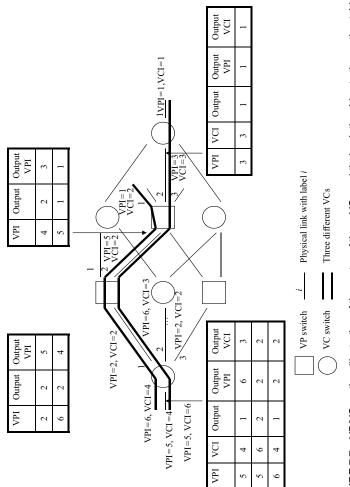

|   |                                                | 7.4.5                                                | Routing Using VCI and VPI                                             | 289        |  |  |  |

|   |                                                | 7.4.6                                                | Motivations for VP/VC Two-Tier Hierarchy                              | 293        |  |  |  |

| <ul> <li>7.6 Transmission Interface</li> <li>7.7 Approaches Toward IP over ATM</li> <li>7.7.1 Classical IP over ATM</li> <li>7.7.2 Next Hop Resolution Protocol</li> <li>7.7.3 IP Switch and Cell Switch Router</li> <li>7.7.4 ARIS and Tag Switching</li> <li>7.7.5 Multiprotocol Label Switching</li> <li>Appendix 7.A ATM Cell Format</li> <li>7.A.1 ATM Layer</li> <li>7.A.2 Adaptation Layer</li> <li>Problems</li> <li>8 Network Traffic Control and Bandwidth Alloo</li> <li>8.1 Fluid-Flow Model: Deterministic Discussion</li> <li>8.2 Fluid-Flow On–Off Source Model: Stochastic</li> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir Access Control</li> <li>8.5 Closed-Loop Flow Control</li> <li>Problems</li> <li>9 Packet Switching and Information Transmission</li> <li>9.1 Duality of Switching and Transmission</li> </ul> | 326                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>7.7.1 Classical IP over ATM</li> <li>7.7.2 Next Hop Resolution Protocol</li> <li>7.7.3 IP Switch and Cell Switch Router</li> <li>7.7.4 ARIS and Tag Switching</li> <li>7.7.5 Multiprotocol Label Switching</li> <li>Appendix 7.A ATM Cell Format</li> <li>7.A.1 ATM Layer</li> <li>7.A.2 Adaptation Layer</li> <li>Problems</li> <li>8 Network Traffic Control and Bandwidth Allog</li> <li>8.1 Fluid-Flow Model: Deterministic Discussion</li> <li>8.2 Fluid-Flow On–Off Source Model: Stochastic</li> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir Access Control</li> <li>8.5 Closed-Loop Flow Control problems</li> <li>9 Packet Switching and Information Transmiss</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                            | 301<br>302<br>303<br>306<br>308<br>311<br>311<br>314<br>319<br>cation 323<br>Treatment 332<br>348<br>354<br>355                   |

| <ul> <li>7.7.2 Next Hop Resolution Protocol</li> <li>7.7.3 IP Switch and Cell Switch Router</li> <li>7.7.4 ARIS and Tag Switching</li> <li>7.7.5 Multiprotocol Label Switching</li> <li>Appendix 7.A ATM Cell Format</li> <li>7.A.1 ATM Layer</li> <li>7.A.2 Adaptation Layer</li> <li>Problems</li> <li>8 Network Traffic Control and Bandwidth Alloo</li> <li>8.1 Fluid-Flow Model: Deterministic Discussion</li> <li>8.2 Fluid-Flow On–Off Source Model: Stochastic</li> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir Access Control</li> <li>8.5 Closed-Loop Flow Control problems</li> <li>9 Packet Switching and Information Transmiss</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                 | 302<br>303<br>306<br>308<br>311<br>311<br>314<br>319<br>cation 323<br>Treatment 322<br>348<br>354<br>355                          |

| <ul> <li>7.7.3 IP Switch and Cell Switch Router</li> <li>7.7.4 ARIS and Tag Switching</li> <li>7.7.5 Multiprotocol Label Switching</li> <li>Appendix 7.A ATM Cell Format</li> <li>7.A.1 ATM Layer</li> <li>7.A.2 Adaptation Layer</li> <li>Problems</li> <li>8 Network Traffic Control and Bandwidth Allow</li> <li>8.1 Fluid-Flow Model: Deterministic Discussion</li> <li>8.2 Fluid-Flow On–Off Source Model: Stochastic</li> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir Access Control</li> <li>8.5 Closed-Loop Flow Control Problems</li> <li>9 Packet Switching and Information Transmiss</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                             | 303<br>306<br>308<br>311<br>311<br>314<br>319<br><b>cation</b><br>326<br>Treatment<br>322<br>348<br>354<br>355                    |

| <ul> <li>7.7.4 ARIS and Tag Switching</li> <li>7.7.5 Multiprotocol Label Switching</li> <li>Appendix 7.A ATM Cell Format</li> <li>7.A.1 ATM Layer</li> <li>7.A.2 Adaptation Layer</li> <li>Problems</li> <li>8 Network Traffic Control and Bandwidth Allow</li> <li>8.1 Fluid-Flow Model: Deterministic Discussion</li> <li>8.2 Fluid-Flow On–Off Source Model: Stochastic</li> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir Access Control</li> <li>8.5 Closed-Loop Flow Control Problems</li> <li>9 Packet Switching and Information Transmiss</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                             | 306<br>308<br>311<br>311<br>314<br>319<br>cation 323<br>Treatment 322<br>348<br>354<br>355                                        |

| <ul> <li>7.7.5 Multiprotocol Label Switching</li> <li>Appendix 7.A ATM Cell Format</li> <li>7.A.1 ATM Layer</li> <li>7.A.2 Adaptation Layer</li> <li>Problems</li> <li>8 Network Traffic Control and Bandwidth Alloo</li> <li>8.1 Fluid-Flow Model: Deterministic Discussion</li> <li>8.2 Fluid-Flow On–Off Source Model: Stochastic</li> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir Access Control</li> <li>8.5 Closed-Loop Flow Control Problems</li> <li>9 Packet Switching and Information Transmiss</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                   | 308<br>311<br>311<br>314<br>319<br>cation 323<br>326<br>Treatment 332<br>348<br>354<br>355                                        |

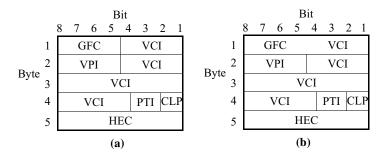

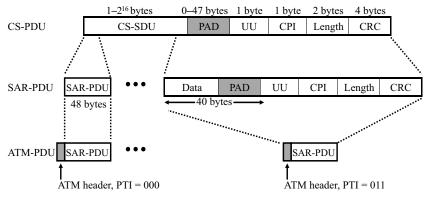

| <ul> <li>Appendix 7.A ATM Cell Format <ul> <li>7.A.1 ATM Layer</li> <li>7.A.2 Adaptation Layer</li> <li>Problems</li> </ul> </li> <li>8 Network Traffic Control and Bandwidth Allow <ul> <li>8.1 Fluid-Flow Model: Deterministic Discussion</li> <li>8.2 Fluid-Flow On–Off Source Model: Stochastic</li> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir Access Control</li> </ul> </li> <li>8.5 Closed-Loop Flow Control problems</li> <li>9 Packet Switching and Information Transmiss <ul> <li>9.1 Duality of Switching and Transmission</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                            | 311<br>311<br>314<br>319<br>cation 323<br>326<br>Treatment 332<br>348<br>354<br>355                                               |

| <ul> <li>7.A.1 ATM Layer</li> <li>7.A.2 Adaptation Layer<br/>Problems</li> <li>8 Network Traffic Control and Bandwidth Allow</li> <li>8.1 Fluid-Flow Model: Deterministic Discussion</li> <li>8.2 Fluid-Flow On–Off Source Model: Stochastic</li> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir<br/>Access Control</li> <li>8.5 Closed-Loop Flow Control<br/>Problems</li> <li>9 Packet Switching and Information Transmis<br/>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                         | 311<br>314<br>319<br>cation 323<br>326<br>Treatment 332<br>348<br>354<br>355                                                      |

| <ul> <li>7.A.2 Adaptation Layer<br/>Problems</li> <li>8 Network Traffic Control and Bandwidth Allow<br/>8.1 Fluid-Flow Model: Deterministic Discussion<br/>8.2 Fluid-Flow On–Off Source Model: Stochastic<br/>8.3 Traffic Shaping and Policing<br/>8.4 Open-Loop Flow Control and Scheduling<br/>8.4.1 First-Come-First-Serve Scheduling<br/>8.4.2 Fixed-Capacity Assignment<br/>8.4.3 Round-Robin Scheduling<br/>8.4.4 Weighted Fair Queueing<br/>8.4.5 Delay Bound in Weighted Fair Queueir<br/>Access Control<br/>8.5 Closed-Loop Flow Control<br/>Problems</li> <li>9 Packet Switching and Information Transmis<br/>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                    | 314<br>319<br>cation 323<br>326<br>Treatment 332<br>348<br>354<br>355                                                             |

| <ul> <li>Problems</li> <li>8 Network Traffic Control and Bandwidth Allow</li> <li>8.1 Fluid-Flow Model: Deterministic Discussion</li> <li>8.2 Fluid-Flow On–Off Source Model: Stochastic</li> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir<br/>Access Control</li> <li>8.5 Closed-Loop Flow Control<br/>Problems</li> <li>9 Packet Switching and Information Transmiss</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                       | 319         cation       323         326         Treatment       332         348         354         355                          |

| <ul> <li>8 Network Traffic Control and Bandwidth Allog</li> <li>8.1 Fluid-Flow Model: Deterministic Discussion</li> <li>8.2 Fluid-Flow On–Off Source Model: Stochastic</li> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir Access Control</li> <li>8.5 Closed-Loop Flow Control Problems</li> <li>9 Packet Switching and Information Transmiss</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 | Scation         323           326         326           Treatment         332           348         354           355         355 |

| <ul> <li>8.1 Fluid-Flow Model: Deterministic Discussion</li> <li>8.2 Fluid-Flow On–Off Source Model: Stochastic</li> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir Access Control</li> <li>8.5 Closed-Loop Flow Control Problems</li> <li>9 Packet Switching and Information Transmise</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 326<br>Treatment 332<br>348<br>354<br>355                                                                                         |

| <ul> <li>8.2 Fluid-Flow On–Off Source Model: Stochastic</li> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir<br/>Access Control</li> <li>8.5 Closed-Loop Flow Control<br/>Problems</li> <li>9 Packet Switching and Information Transmis<br/>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Treatment 332<br>348<br>354<br>355                                                                                                |

| <ul> <li>8.3 Traffic Shaping and Policing</li> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir<br/>Access Control</li> <li>8.5 Closed-Loop Flow Control<br/>Problems</li> <li>9 Packet Switching and Information Transmise</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 348<br>354<br>355                                                                                                                 |

| <ul> <li>8.4 Open-Loop Flow Control and Scheduling</li> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir<br/>Access Control</li> <li>8.5 Closed-Loop Flow Control<br/>Problems</li> <li>9 Packet Switching and Information Transmise</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 354<br>355                                                                                                                        |

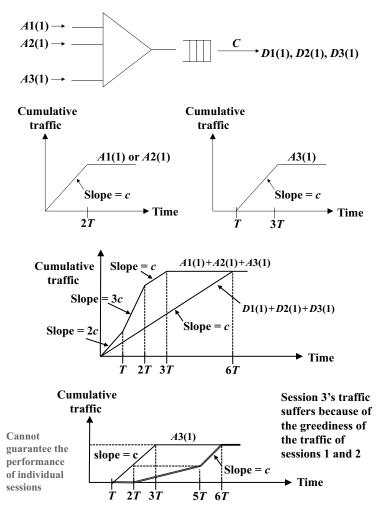

| <ul> <li>8.4.1 First-Come-First-Serve Scheduling</li> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir<br/>Access Control</li> <li>8.5 Closed-Loop Flow Control<br/>Problems</li> <li>9 Packet Switching and Information Transmise</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 355                                                                                                                               |

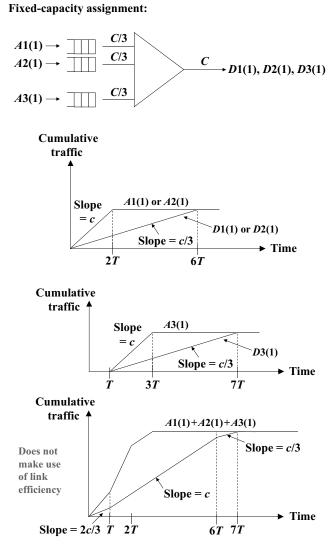

| <ul> <li>8.4.2 Fixed-Capacity Assignment</li> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir<br/>Access Control</li> <li>8.5 Closed-Loop Flow Control<br/>Problems</li> <li>9 Packet Switching and Information Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |

| <ul> <li>8.4.3 Round-Robin Scheduling</li> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir<br/>Access Control</li> <li>8.5 Closed-Loop Flow Control<br/>Problems</li> <li>9 Packet Switching and Information Transmise</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 357                                                                                                                               |

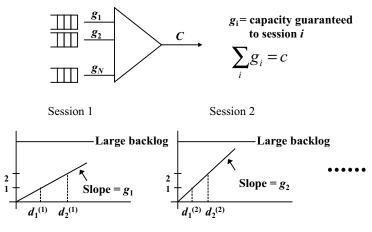

| <ul> <li>8.4.4 Weighted Fair Queueing</li> <li>8.4.5 Delay Bound in Weighted Fair Queueir<br/>Access Control</li> <li>8.5 Closed-Loop Flow Control<br/>Problems</li> <li>9 Packet Switching and Information Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   |

| <ul> <li>8.4.5 Delay Bound in Weighted Fair Queueir<br/>Access Control</li> <li>8.5 Closed-Loop Flow Control<br/>Problems</li> <li>9 Packet Switching and Information Transmis<br/>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 358                                                                                                                               |

| Access Control<br>8.5 Closed-Loop Flow Control<br>Problems<br>9 Packet Switching and Information Transmis<br>9.1 Duality of Switching and Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 364                                                                                                                               |

| <ul> <li>Problems</li> <li>9 Packet Switching and Information Transmis</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | g with Leaky-Bucket 373                                                                                                           |

| <ul> <li>Problems</li> <li>9 Packet Switching and Information Transmis</li> <li>9.1 Duality of Switching and Transmission</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 380                                                                                                                               |

| 9.1 Duality of Switching and Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 381                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | sion 385                                                                                                                          |

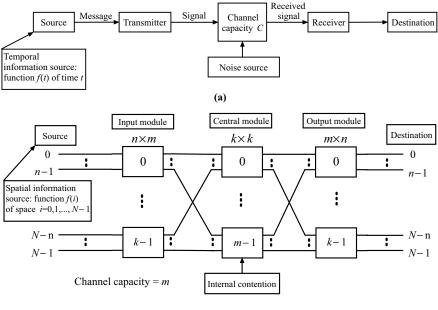

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 386                                                                                                                               |

| 9.2 Parallel Characteristics of Contention and Nois                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | se 390                                                                                                                            |

| 9.2.1 Pseudo Signal-to-Noise Ratio of Packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Switch 390                                                                                                                        |

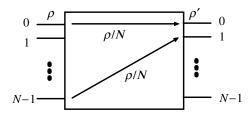

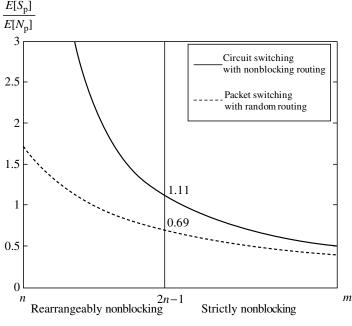

| 9.2.2 Clos Network with Random Routing as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | a Noisy Channel 393                                                                                                               |

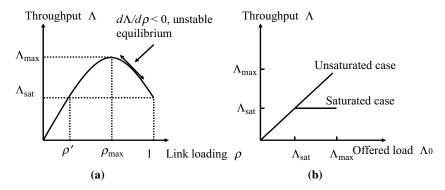

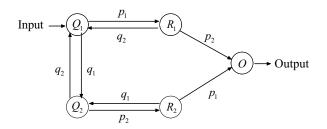

| 9.3 Clos Network with Deflection Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 396                                                                                                                               |

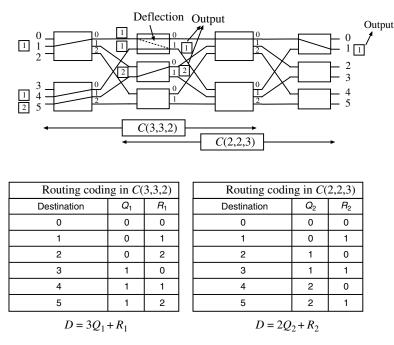

| 9.3.1 Cascaded Clos Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 397                                                                                                                               |

| 9.3.2 Analysis of Deflection Clos Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 397                                                                                                                               |

| 9.4 Route Assignments and Error-Correcting Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                   |

| 9.4.1 Complete Matching in Bipartite Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | es 402                                                                                                                            |

| 9.4.2 Graphical Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   |

| 9.4.3 Route Assignments of Benes Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                   |

| 433 |

|-----|

| 430 |

| 424 |

| 420 |

| 417 |

| 416 |

| 414 |

| 411 |

| 410 |

|     |

## PREFACE

The past few decades have seen the merging of many computer and communication applications. Enabled by the advancement of optical fiber, wireless communication, and very-large-scale integration (VLSI) technologies, modern telecommunication networks can be regarded as one of the most important inventions of the past century.

Before the emergence of Broadband Integrated Services Digital Network (B-ISDN), several separate communication networks already existed. They include the telephone network for voice communication, the computer network for data communication, and the television network for TV program broadcasting. These networks are designed with a specific application in mind and are typically not well suited for other applications. For example, the conventional telephone network cannot carry high-speed multimedia services, which require diverse quality-of-service (QoS) guarantees to support multirate and multicast connections. In addition, these heterogeneous networks often require expensive gateways equipped with different access interfaces running different protocols.

Meanwhile, the appeal of interactive video communication is on the rise in a society that is increasingly information-oriented. Images and facial expressions are more vivid and informative than text and audio for many types of human interactions. For example, video conferencing has made distant learning, medicine, and surgery possible, while 3D Internet games give rise to real-time interactions between remote players. All these applications are based on high-resolution video with large bandwidth demands. These developments led to the emergence of B-ISDN—the concept of an integrated network to support communication services of all kinds to achieve the most cost-effective sharing of resources was conceived in the late 1980s.

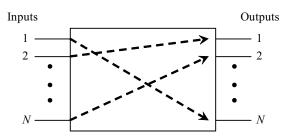

This book focuses on the design and analysis of switch architectures that are suitable for broadband integrated networks. In particular, the emphasis is on packetswitched interconnection networks with distributed routing algorithms. The focus is on the mathematical properties of these networks rather than specific implementation technologies. As such, although the pedagogical explanations in this book are in the context of switches, many of the fundamental principles are relevant to other communication networks with regular topologies. For example, the terminals in a multi-hop ad hoc wireless network could conceivably be interconnected together to form a logical topology that is regular. This could be enabled by the use of directional antennas, inexpensive multi-radio, and cognitive-radio technologies that can identify unused spectra. These technologies allow links to be formed among the terminals in a more flexible way, not necessarily based on proximity alone. There are two main advantages to regular network topologies: (1) very simple routing and scheduling are possible with their well-understood mathematical properties; and (2) performance and behavior are well understood and predictable. The performance and robustness of these ad hoc networks are by no means ad hoc.

The original content of this book was an outgrowth of an evening course offered at the Electrical Engineering Department of Columbia University, New York, in 1989. Since then, this course has been taught at Polytechnic Institute of New York University, Brooklyn, NY and the Chinese University of Hong Kong, Hong Kong. The target audience is senior undergraduate and first-year postgraduate students with solid background in probability theory. We found that many of our former students acquired an appreciation of the beauty of the mathematics associated with telecommunication networks after taking courses based on this book.

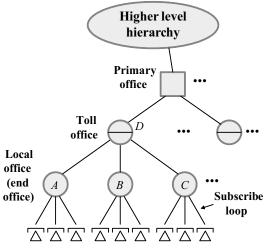

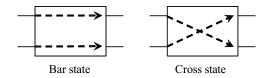

A general introduction and an overview of the entire book are given in Chapter 1, in which the roles of switching and transmission in the computer networks and telephone networks are discussed. The concept of the modern broadband integrated services network is explained and the reasons why this concept is necessary in modern society are also given in this chapter. The focus of Chapter 2 is on circuit switch design principles. Two types of the circuit switch design—space domain and time domain—are introduced in this chapter. Several classical nonblocking networks, including Clos network, Benes network, and Cantor network, are discussed.

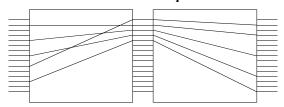

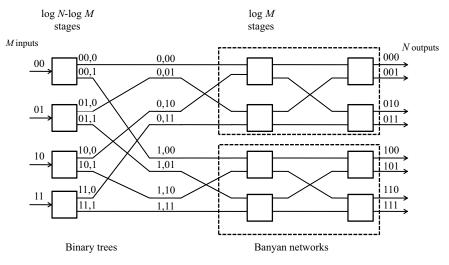

Chapter 3 is devoted to fundamental principles of packet switch design, and Chapter 4 focuses on the throughput and delay analyses of both waiting and loss switching systems. The nonblocking and self-routing properties of packet switches are elaborated by the combination of sorting and Banyan networks. Throughput improvements are illustrated by some switch design variations such as speedup principle, channel-grouping principle, knockout principle, and dilation principle.

Chapter 5, following the previous chapter, explains some advanced switch design principles to alleviate the packet contention problem. Several networks based on the deflection routing principle such as tandem-banyan, shuffle-exchange, feedback shuffle-exchange, feedback bidirectional shuffle-exchange, and dual shuffle-exchange are introduced. Switch scalability is discussed, which provides some key principles to the construction of large switches out of modest-size switches, without sacrificing overall switch performance. Chapter 6, on switch design principles for broadband services, first presents several fundamental switch design principles for multicasting. Then we end the chapter by introducing the concept of path switching, which is a compromise of the dynamic and the static routing schemes.

Chapter 7 departs from switch designs and the focus moves to broadband communication networks that make use of such switches. The asynchronous transfer mode (ATM) being standardized worldwide is the technology that meets the requirements of the broadband communication networks. ATM is a switching technology that divides data into fixed-length packets called cells. Chapter 8, on network traffic control and bandwidth allocation, gives an introduction on how to allocate network resources and control the traffic to satisfy the quality-of-service (QoS) requirements of network users and to maximize network usage.

The content of Chapter 9 is an article "The mathematical parallels between packet switching and information transmission" originally posted at http://arxiv.org/abs/cs/0610050, which is included here as an epilogue. It is clear from the title that this is a philosophical discussion of analogies between switching and transmission. We show that transmission noise and packet contention actually have similar characteristics and can be tamed by comparable means to achieve reliable communication. From various comparisons, we conclude that packet switching systems are governed by mathematical laws that are similar to those of digital transmission systems as envisioned by Shannon in his seminal 1948 BSTJ paper "A Mathematical Theory of Communication."

We would like to thank many former students of Broadband Communication Laboratory at the Chinese University of Hong Kong, including Cheuk H. Lam, Philip To, Man Chi Chan, Cathy Chan, Soung-Yue Liew, Yun Deng, Manting Choy, Jianming Liu, Sichao Ruan, Li Pu, Dongjie Yin, and Pui King Wong, who participated in the discussions of the content of the book over the years. We are especially grateful for the delicate latex editing and figure drawing of the entire book by our student assistants Jiawei Chen and Yulin Deng. Our "family networks," though small, have given us the connectivity to many joys of life. We can never repay the debt of gratitude we owe to our families—our wives, Alice and So Kuen, and our children, Wynne and Edward Lee, and Vincent and Austin Liew—for their understanding, support, and patience while we wrote this book.

> TONY T. LEE SOUNG C. LIEW

## ABOUT THE AUTHORS

**Professor Tony T. Lee** received his BSEE degree from the National Cheng Kung University, Taiwan, in 1971, and his MS and PhD degrees in electrical engineering from the Polytechnic University in New York in 1976 and 1977, respectively. Currently, he is a Professor of Information Engineering at the Chinese University of Hong Kong and an Adjunct Professor at the Institute of Applied Mathematics of the Chinese Academy of Sciences. From 1991 to 1993, he was a Professor of Electrical Engineering at the Polytechnic Institute of University of New York, Brooklyn, NY. He was with AT&T Bell Laboratories, Holmdel, NJ, from 1977 to 1983, and Bellcore, currently Telcordia Technologies, Morristown, NJ, from 1983 to 1993. He is now serving as an Editor of the *IEEE Transactions on Communications*, and an Area Editor of *Journal of Communication Network*. He is a fellow of IEEE and HKIE. He is the recipient of many awards including the National Natural Science Award from China, the Leonard G. Abraham Prize Paper Award from the IEEE Communication Society, and the Outstanding Paper Award from IEICE.

Professor Soung Chang Liew received his SB, SM, EE, and PhD degrees from the Massachusetts Institute of Technology. From 1984 to 1988, he was at the MIT Laboratory for Information and Decision Systems, where he investigated fiber-optic communication networks. From March 1988 to July 1993, Professor Liew was at Bellcore (now Telcordia), New Jersey, where he was engaged in broadband network research. He is currently Professor and Chairman of the Department of Information Engineering, the Chinese University of Hong Kong. He is also an Adjunct Professor at the Southeast University, China. His current research interests include wireless networks, Internet protocols, multimedia communications, and packet switch design. Professor Liew and his students won the best paper awards at the 1st IEEE International Conference on Mobile Ad-Hoc and Sensor Systems (IEEE MASS 2004) and the 4th IEEE International Workshop on Wireless Local Network (IEEE WLN 2004). Separately, TCP Veno, a version of TCP to improve its performance over wireless networks proposed by Professor Liew and his students, has been incorporated into a recent release of Linux OS. In addition, Professor Liew initiated and built the first interuniversity ATM network testbed in Hong Kong in 1993.

Besides academic activities, Professor Liew is active in the industry. He cofounded two technology start-ups in Internet software and has been serving as consultant to many companies and industrial organizations. He is currently consultant for the Hong Kong Applied Science and Technology Research Institute (ASTRI), providing technical advice as well as helping to formulate R&D directions and strategies in the areas of wireless internetworking, applications, and services. Professor Liew holds three U.S. patents and is a Fellow of IEE and HKIE. He is listed in Marquis Who's Who in Science and Engineering. He is the recipient of the first Vice-Chancellor Exemplary Teaching Award at the Chinese University of Hong Kong.

1

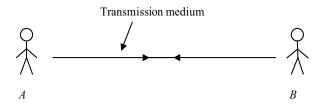

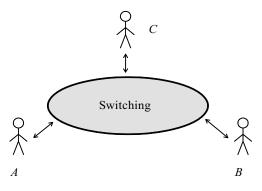

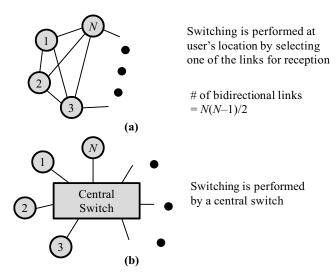

## INTRODUCTION AND OVERVIEW

The past few decades have seen the merging of computer and communication technologies. Wide-area and local-area computer networks have been deployed to interconnect computers distributed throughout the world. This has led to a proliferation of many useful data communication services, such as electronic mail, remote file transfer, remote login, and web pages. Most of these services do not have very stringent "realtime" requirements in the sense that there is no urgency for the data to reach the receiver within a very short time, say, below 1s. At the other spectrum, the telephone network has been with us for a long time, and the information carried by the network has been primarily real-time telephone conversations. It is important for voice to reach the listener almost immediately for an intelligible and coherent conversation to take place.

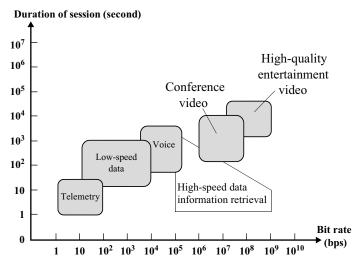

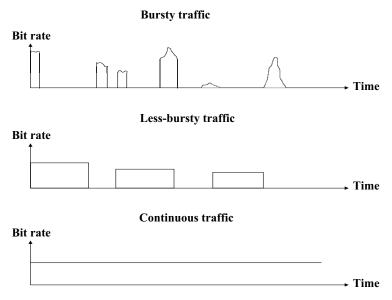

With the emergence of multimedia services, real-time traffic will include not just voice, but also video, image, and computer data files. This has given rise to the vision of an integrated broadband network that is capable of carrying all kinds of information, real-time or non-real-time.